Nº d'ordre : 300 Année 2000

## **THESE**

présentée en vue de l'obtention du titre de

#### **DOCTEUR**

de

### L'ECOLE NATIONALE SUPERIEURE DE L'AERONAUTIQUE ET DE L'ESPACE

SPECIALITE: Microélectronique, Capteurs d'Images

par

## Yavuz DEGERLI

Etude, modélisation des bruits et conception des circuits de lecture dans les capteurs d'images à pixels actifs CMOS

Soutenue le 6 octobre 2000 devant la Commission d'Examen :

MM. J. **GRAFFEUIL** Président F. LAVERNHE G. LECOY Rapporteur P. MAGNAN Directeur de thèse Ρ. MARCHEGAY Rapporteur **SAINT-PE** Ο.

#### Titre:

Etude, modélisation des bruits et conception des circuits de lecture dans les capteurs d'images à pixels actifs CMOS.

#### Résumé:

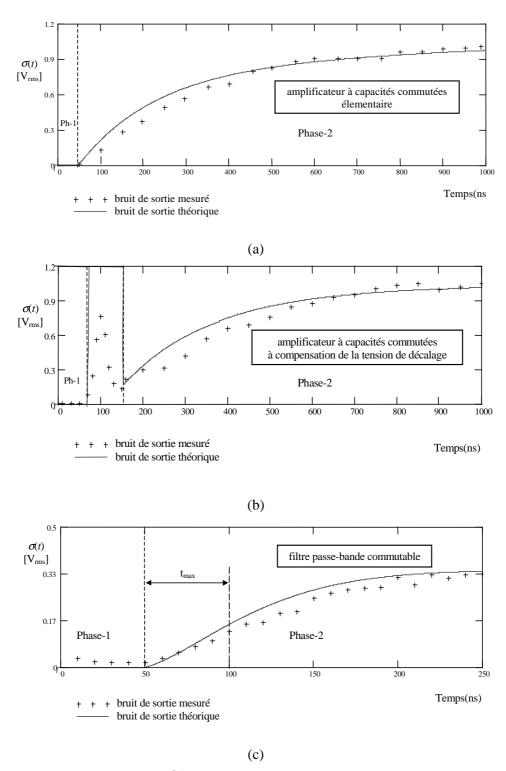

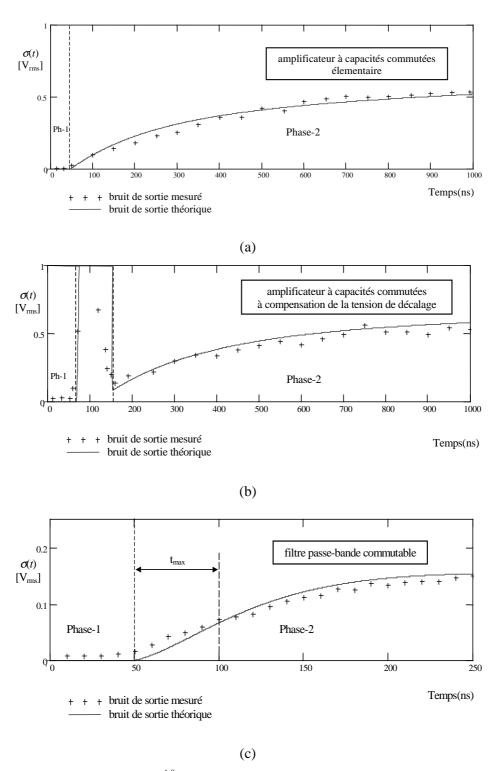

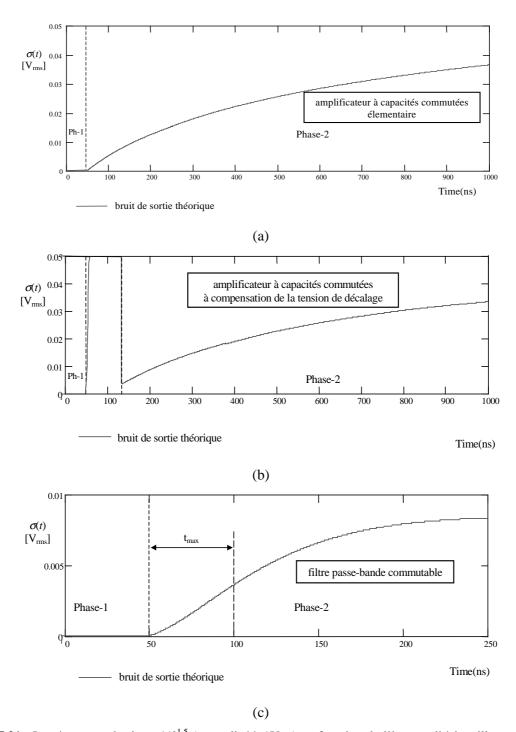

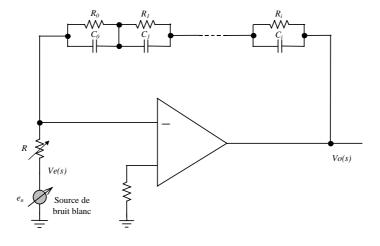

Ce travail porte sur l'amélioration des performances en bruit et sur la conception de circuits de lecture de capteurs d'images à pixels actifs CMOS à destination des applications scientifiques. La première partie est consacrée à l'étude et à la modélisation du bruit temporel de la chaîne de lecture du capteur. Cette étude nous permet de définir des règles de conception réduisant le bruit de ces circuits. Des circuits de test ont été réalisés sur une technologie CMOS 0.7µm, afin de valider les résultats obtenus. Le deuxième axe porte sur la conception de circuits analogiques de lecture et de traitement du signal effectuant l'extraction du signal utile, l'amplification, et la correction de bruit spatial fixe de colonnes, intégrés sur la même puce que la matrice photosensible ainsi que l'analyse de leurs performances. Trois circuits ont été réalisés sur une technologie CMOS 0.7µm: le premier est un amplificateur à capacités commutées (c.c.) élémentaire, le second un amplificateur à c.c. à compensation de la tension de décalage, et le troisième un filtre passe-bande actif commutable. Ils permettent des vitesses de lecture jusqu'à 10 Mpixel/sec. Une analyse théorique détaillée de la réponse des circuits au bruit blanc et au bruit en  $1/f^{\alpha}$ , en considérant la nature non-stationnaire des signaux de sortie, est présentée. Les résultats expérimentaux et théoriques sont comparés. Finalement un nouveau circuit de lecture du signal des colonnes est proposé et développé afin de réduire le bruit spatial fixe de colonnes. Il nécessite un seul amplificateur de colonne commun à toute une matrice de pixels. Les effets des non-idéalités des composants réels sur les performances de ce circuit sont étudiés et des solutions sont proposées et discutées afin de les minimiser. Les résultats expérimentaux ainsi que les problèmes rencontrés sur un circuit de test, comprenant 128x128 pixels et réalisé sur une technologie CMOS 0.6µm, sont présentés.

#### Mots clés:

Capteur d'images, APS, double échantillonnage corrélé, circuit de lecture, capacités commutées, bruit thermique, bruit en 1/f, filtre passe-bande actif commutable, modèle diffusif.

#### Title:

Design of readout circuitry and analysis of temporal noise in CMOS active pixel image sensors

#### Abstract:

This work is focused on the improvement of noise performances and the design of readout circuitry of CMOS active pixels sensors. In the first part of this thesis, the analytical noise analysis of correlated double sampling (CDS) readout circuits used in CMOS active pixel image sensors is presented. Both low frequency noise and thermal noise are considered. The results allow us to optimize the MOS transistor dimensions and capacitor values for lower noise, with the help of SPICE-based circuit simulators. Test circuits were fabricated on a CMOS 0.7µm process to validate the results. A good agreement was observed between experimental and analytical results. Then, three analog signal processing circuits are proposed for CMOS active pixel imagers, used to extract the signal level proportional to the incident light, amplify it, and to suppress the column FPN (Fixed Pattern Noise). They are based on a fully differential cascode operational transconductance amplifier, and implemented on a CMOS 0.7µm process: the first is an uncompensated SC (Switched Capacitor) voltage amplifier; the second an offset-compensated SC amplifier, and the third a commutable band-pass filter. They offer up to 10Mpixels/s readout rates. A detailed theoretical analysis of the amplifiers response to white noise and low frequency noise is given, considering the non-stationary nature of the output signals. A method based on diffusive Markovian representation of  $1/f^{\alpha}$ -noise is used. The theoretical results are compared with experimental data. Finally, a new column readout circuit is presented. The proposed circuit is simple and requires only one output amplifier. It is based on capacitor ratios rather than MOS transistor matching, reducing the column FPN. The effects of the imperfections of the components on the performance of the circuit are investigated. Experimental results obtained on a test circuit comprising an 128x128 pixels array designed on a CMOS 0.6μm process are discussed.

#### **Keywords:**

APS, CMOS image sensor, correlated-double sampling, CDS, thermal noise, 1/f noise, flicker noise, readout circuit, switched-capacitor circuit.

#### Remerciements...

Les travaux présentés dans ce mémoire ont été effectués au sein du laboratoire de recherche **CIMI** (Conception d'Imageurs Matriciels Intégrés) de l'Ecole Nationale Supérieure de l'Aéronautique et de l'Espace (**SUPAERO**) à Toulouse.

Tout d'abord, je tiens à remercier les membres du jury, tout particulièrement Monsieur Jacques GRAFFEUIL, Professeur à l'Université Paul Sabatier à Toulouse, qui m'a fait l'honneur de le présider. Tous mes remerciements vont également à Messieurs Gilles LECOY, Professeur à l'Université Montpellier II, et Philippe MARCHEGAY, Professeur et Directeur de l'Ecole Nationale Supérieure d'Electronique et de Radioélectricité de Bordeaux, pour avoir accepté d'être les rapporteurs de cette thèse. Je suis très reconnaissant envers Monsieur Olivier SAINT-PE, ingénieur R&D, spécialiste des détecteurs à ASTRIUM SAS (anciennement Matra Marconi Space) à Toulouse, pour sa participation au jury de cette thèse.

Je remercie Monsieur **Jean FARRE**, Professeur à SUPAERO, fondateur du Laboratoire CIMI, et à la retraite depuis peu de temps, avec qui mes rapports furent aussi divers qu'enrichissants... Il n'a jamais douté un seul instant que je deviendrais ministre...

Je remercie Monsieur **Pierre MAGNAN**, Professeur à SUPAERO, nouveau responsable du Laboratoire CIMI, et directeur de cette thèse, pour sa disponibilité et toutes les vives discussions que l'on a pu avoir, avec qui je partage le même intérêt pour la littérature scientifique...

Je tiens à remercier Monsieur **Francis LAVERNHE**, Professeur en classe préparatoire aux grandes écoles au Lycée Déodat de Séverac, Toulouse, et Professeur associé à SUPAERO, qui m'a dirigé tout au long de ce travail, pour toutes les discussions fructueuses aussi bien scientifiques que politiques, historiques (histoire des turcs...), sociales, religieuses, etc. J'ai toujours eu grand plaisir à travailler avec lui...

Je voudrais remercier mes compagnons de bureau, les thésards actuels du laboratoire CIMI, Anne GAUTRAND (fraîchement doctoresse...), Cécile MARQUES (et son copain Eric...), Stéphan MAËSTRE (et ses CDs sanguinaires..), ainsi que mes voisins de bureau, heureux dans leur salle aujourd'hui climatisée, Franck CORBIERE (et ses questions à 2 francs...), Philippe MARTIN-GONTHIER, les ingénieurs CIMI, pour les moments agréables qu'on a passés ensemble, pour les pauses-cafés, etc...

N'oublions pas non plus les ex-thésards du CIMI: **Cyril CAVADORE**, monsieur l'astronome, maintenant spécialiste des détecteurs CCD à l'ESO (European Southern Observatory) à Munich, pour les soirées qu'on a passées à l'école à découvrir le logiciel CADENCE..., ainsi que **Johannes SOLHUSVIK**, monsieur PHOTOBIT-Norvège, pour son aide au début de ma thèse.

Je tiens à remercier tous les stagiaires et thésards actuels et anciens du Département d'Electronique, Optronique et Physique à SUPAERO, et plus spécialement Olivier TICO, Magali MENARDO, Christophe MOORLAS, Somsak AKATIMAGOOL, René J. LANDRY, Carlos MIRANDA, Patrick SCUDIER, Jean-Marie EVENOU, Magali ESTRIBEAU, Philippe MAURY et tous ceux qui ne sont pas cités ici, pour les moments agréables qu'on a passés ensemble...

Je voudrais en particulier remercier:

Monsieur André BOURRICAUD, chef du Laboratoire d'Electronique, ainsi que les techniciens, Etienne PERRIN, Francisco FRANCHETTI, Thierry SOULET, Francis FROIN, Gérard ROOU, et les autres, Fabien DESTIC, ingénieur de recherche, pour leur aide concernant tous les problèmes techniques,

Pascal GOUJON, qui a toujours su trouver des solutions à tous mes problèmes informatiques (ou presque...),

Vincent CALMETTES et son épouse Béatriz BOTERO, Philippe GUILLOT, pour leur amitié,

Monsieur **Serge BERTRAND**, responsable de la bibliothèque de SUPAERO, pour avoir acheté sans trop râler les 150 bouquins que l'on a commandés, et pour son aide à monter la bibliothèque-bis au CIMI,... ainsi que le personnel de la bibliothèque, Monsieur **Michel REGESTE** et Madame **Odile RITEAU**,

Richard FABRE, et Christian TAKALI (pour leurs compétences photographiques...),

**Ilker YALÇIN**, élève ingénieur à SUPAERO, pour son amitié et son aide concernant la rédaction du manuscrit,

Mes potes en Turquie, surtout ceux qui n'ont pas cessé de m'envoyer des mails,

Enfin, mes derniers remerciements vont à ma famille, et à mon papa qui nous a quittés et n'a pas pu voir la fin de ce travail...

A ma famille.

A la mémoire des victimes du séisme catastrophique en Turquie (août 1999).

# Table des matières

| Introduction                                                                                 | 1  |

|----------------------------------------------------------------------------------------------|----|

| Chapitre I:                                                                                  |    |

| Les Capteurs d'images du CCD à l'APS : Aspects généraux et bruit                             | 5  |

| 1.1 Le capteur CCD                                                                           | 5  |

| 1.2 Le capteur APS                                                                           | 8  |

| 1.2.1 Introduction                                                                           | 8  |

| 1.2.2 Architecture générale d'une matrice APS                                                | 9  |

| 1.2.2.1 Le pixel                                                                             | 9  |

| 1.2.2.2 Circuits de lecture colonne                                                          | 15 |

| 1.2.2.3 Décodeurs d'adresses                                                                 | 17 |

| 1.2.2.4 Chronogramme de lecture de l'APS                                                     | 18 |

| 1.3 Aspects généraux sur le bruit                                                            | 20 |

| 1.3.1 Généralités                                                                            | 20 |

| 1.3.2 Bruit temporel                                                                         | 22 |

| 1.3.2.1 Terminologie                                                                         | 22 |

| 1.3.2.2 Bruit thermique                                                                      | 24 |

| 1.3.2.3 Bruit de grenaille                                                                   | 25 |

| 1.3.2.4 Bruit en 1/f (bruit de scintillement ou "flicker noise")                             | 26 |

| 1.4 Sources de bruit dans l'APS                                                              | 27 |

| 1.4.1 Bruit de grenaille généré par les photons (bruit photonique)                           | 27 |

| 1.4.2 Courant d'obscurité et bruit de grenaille généré par le courant d'obscurité            | 27 |

| 1.4.3 Bruit fixe (ou spatial) de la chaîne de lecture                                        | 28 |

| 1.4.4 Bruit temporel de lecture                                                              | 30 |

| Objective III                                                                                |    |

| Chapitre II :  Analyse et réduction du bruit temporel de la chaîne de lecture du capteur APS | 35 |

|                                                                                              |    |

| 2.1 Introduction                                                                             | 35 |

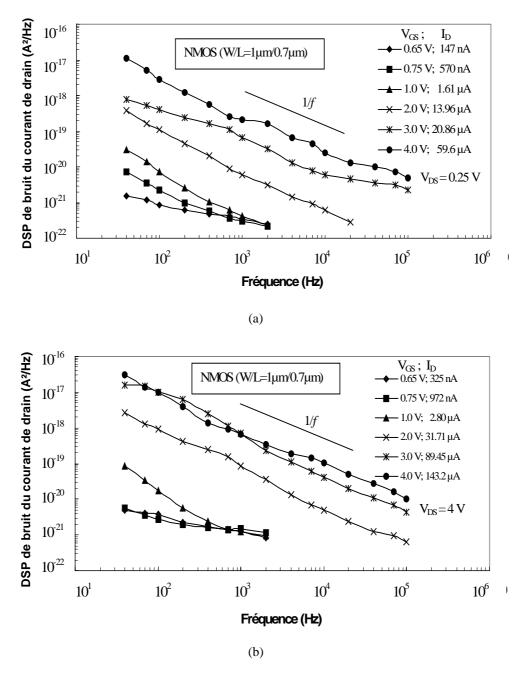

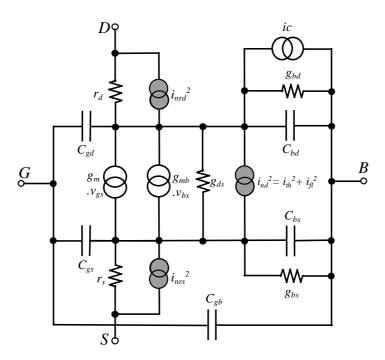

| 2.2 Modèles de bruit pour le transistor MOS                                                  | 40 |

| 2.2.1 Modèles de bruit thermique                                                             | 41 |

| 2.2.2 Modèles de bruit en $1/f$                                                              | 42 |

| 2.3 Analyse de la DSP de bruit total des suiveurs                                       | 43 |

|-----------------------------------------------------------------------------------------|----|

| 2.3.1 Suiveur NMOS du pixel                                                             | 43 |

| 2.3.2 Suiveur PMOS de colonne                                                           | 45 |

| 2.4 Analyse du bruit RMS de sortie avec le procédé CDS                                  | 47 |

| 2.4.1 Effet du CDS sur la variance de sortie                                            | 47 |

| 2.4.2 Contribution du suiveur NMOS de pixel                                             | 51 |

| 2.4.3 Contribution des suiveurs PMOS de colonne                                         | 52 |

| $2.4.4$ Contribution du transistor de reset ou remise à zéro $(M_{RST})$                | 52 |

| 2.4.5 Bruit différentiel total de sortie et bruit ramené à l'entrée avec le procédé CDS | 53 |

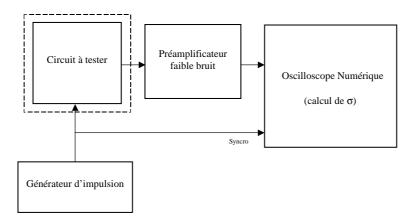

| 2.5 Analyse du bruit RMS de sortie sans le procédé CDS                                  | 54 |

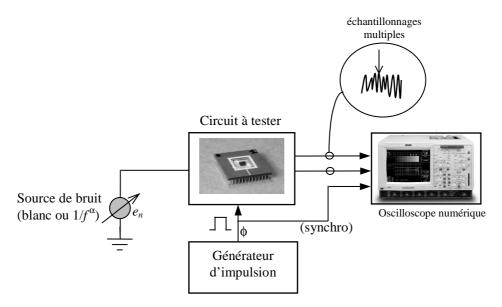

| 2.6 Circuits de test et banc de mesure                                                  | 55 |

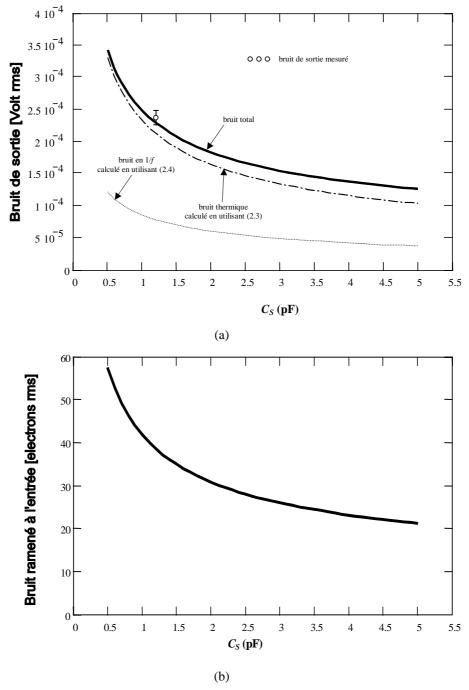

| 2.7 Résultats et discussions                                                            | 56 |

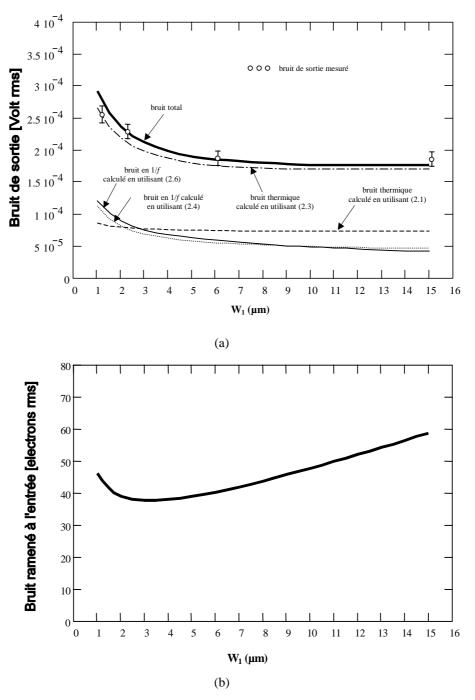

| 2.7.2 Influence de la largeur du canal $(W_I)$                                          | 57 |

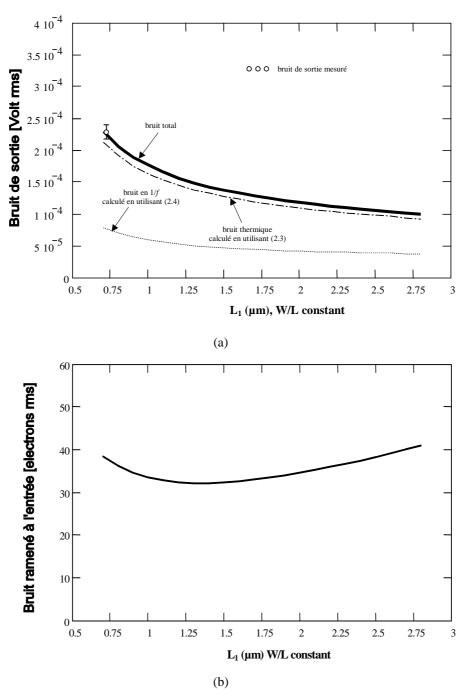

| 2.7.3 Influence de la longueur du canal $(L_I)$                                         | 58 |

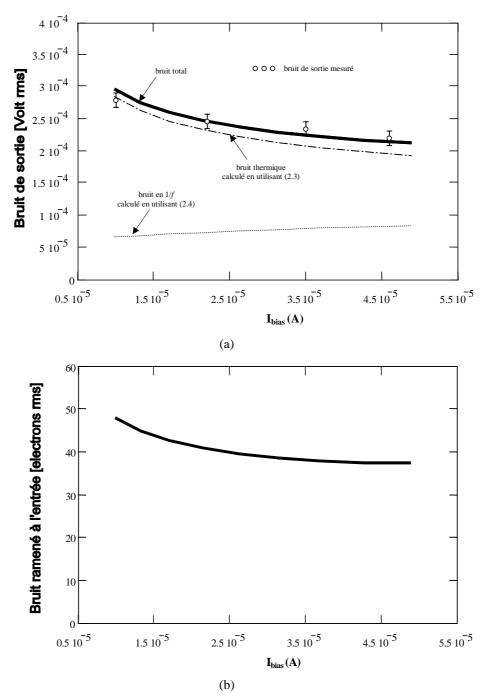

| 2.7.4 Influence du courant de polarisation ( $I_{bias}$ )                               | 59 |

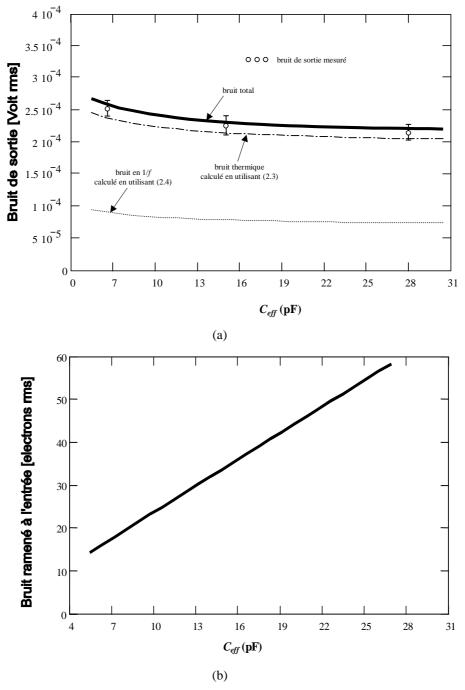

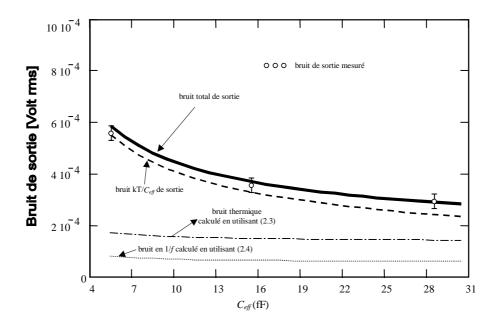

| $2.7.5$ Influence de la capacité de diffusion effective ( $C_{eff}$ )                   | 61 |

| 2.7.6 Influence de la capacité d'échantillonnage ( $C_{ref}$ ou $C_{sig}$ )             | 62 |

| 2.7.7 Bruit de reset (ou bruit kT/C)                                                    | 63 |

| 2.8 Conclusions                                                                         | 63 |

| Chapitre III :                                                                          |    |

| Conception de circuits de traitement pour la chaîne de lecture du capteur APS           | 69 |

| 3.1 Introduction                                                                        | 69 |

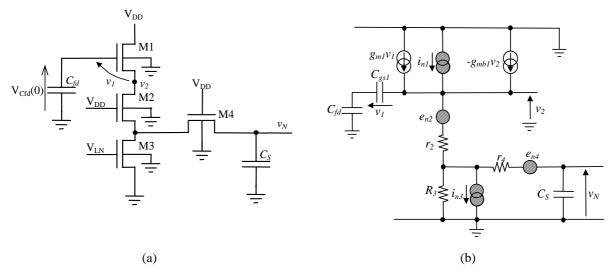

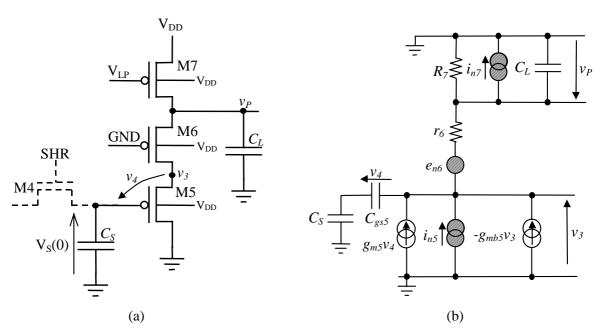

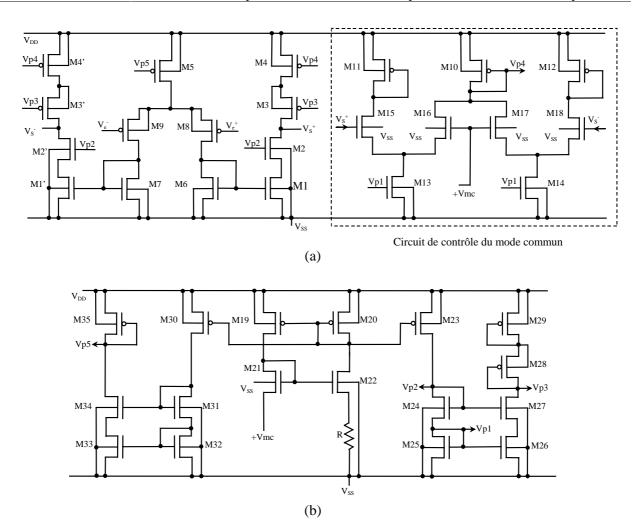

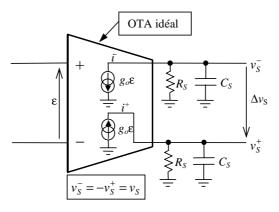

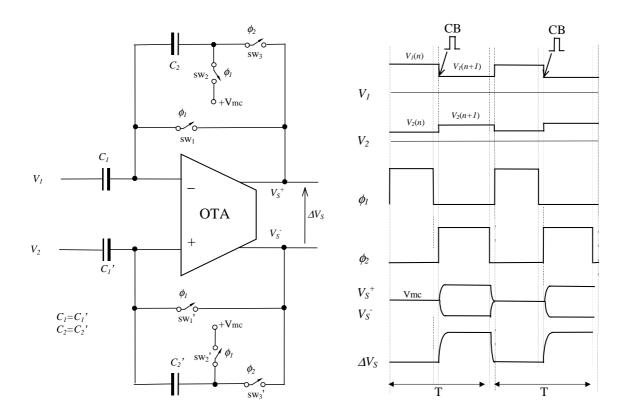

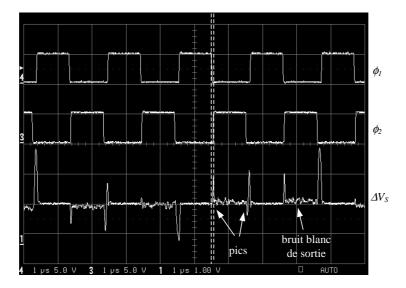

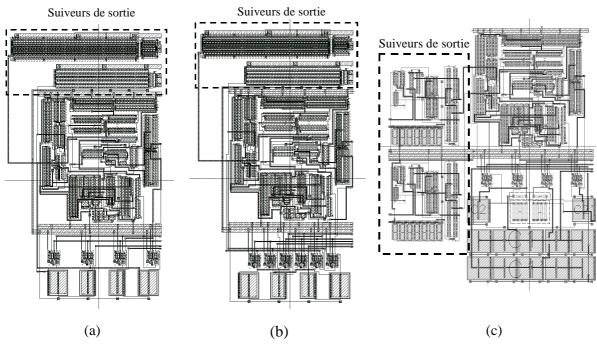

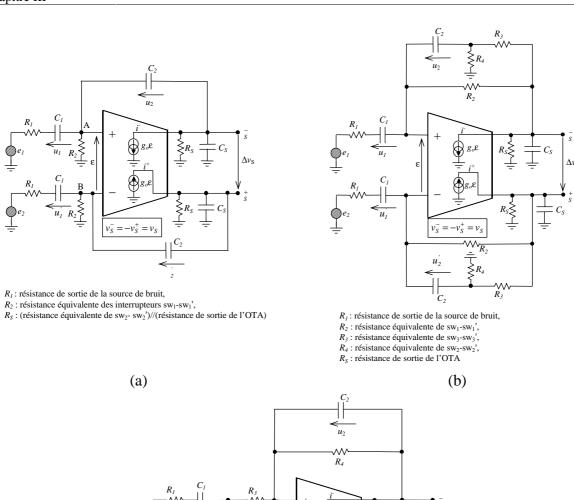

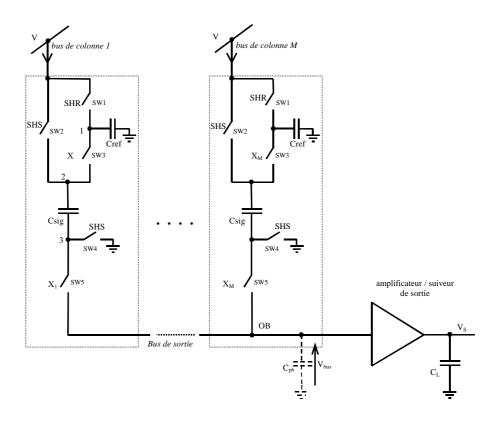

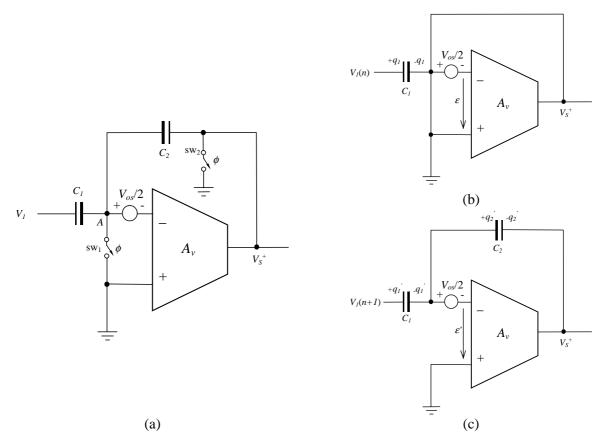

| 3.2 Présentation des circuits                                                           | 72 |

| 3.2.1 Amplificateur de tension à c.c. élémentaire                                       | 74 |

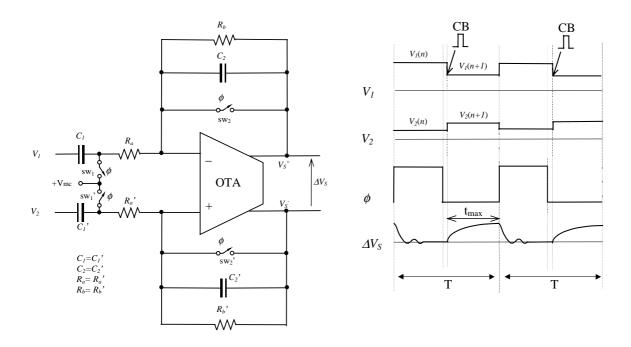

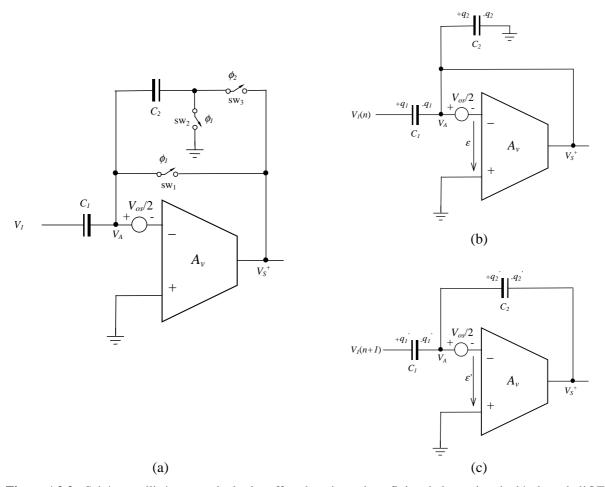

| 3.2.2 Amplificateur de tension à c.c. à compensation de la tension de décalage de l'OTA | 76 |

| 3.2.3 Filtre passe-bande actif commutable                                               | 77 |

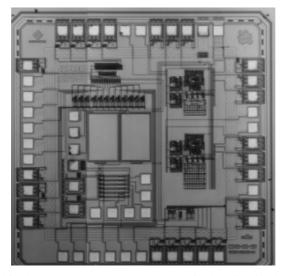

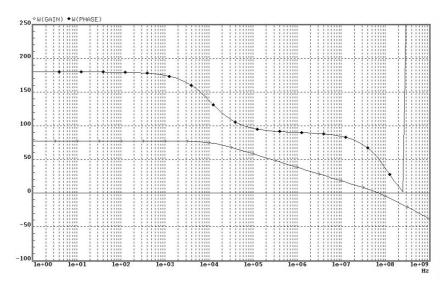

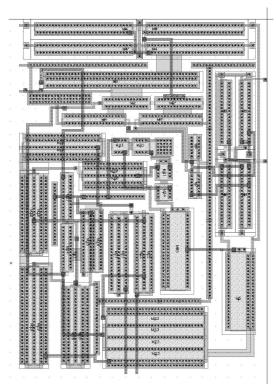

| 3.3 Réalisations des circuits                                                           | 80 |

| 3.4 Equations d'état des circuits                                                       | 81 |

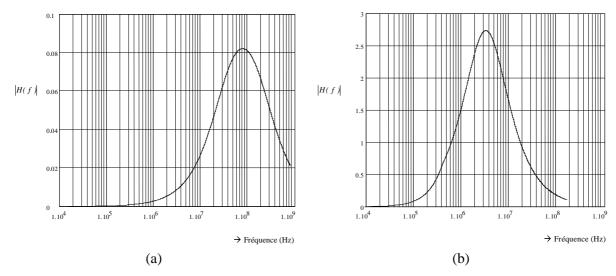

| 3.5 Analyse des réponses en bruit                                                       | 84 |

| 3.5.2 Analyse de la réponse en bruit blanc                                              | 88 |

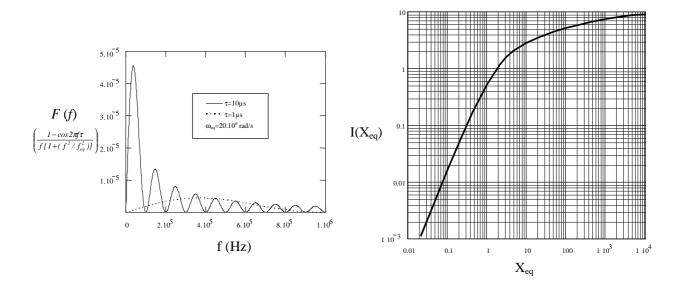

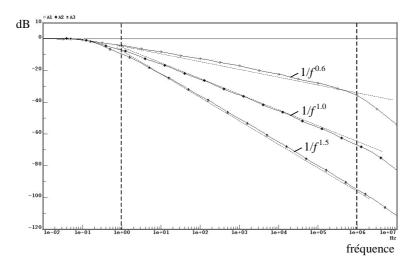

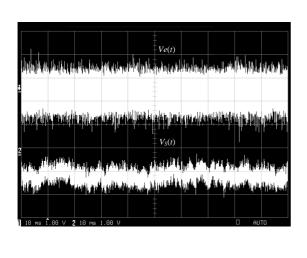

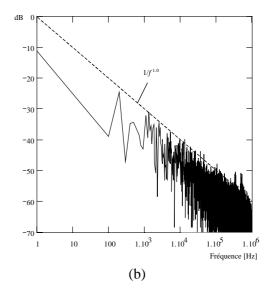

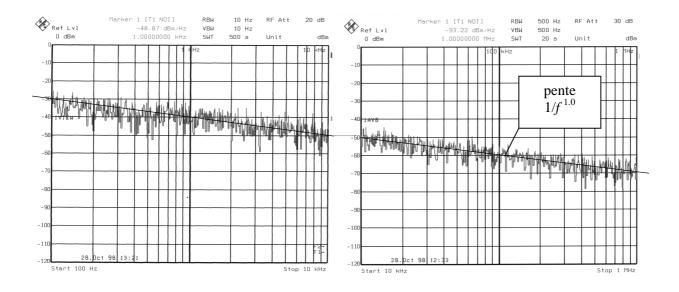

| 3.5.3 Analyse de la réponse au bruit en $1/f^{\alpha}$                                  | 91 |

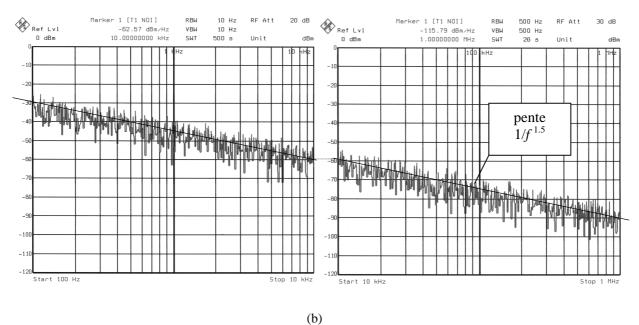

| 3.6 Réalisation d'un générateur de bruit en $1/f^{\alpha}$                                                                                                                          | 99  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.7 Conclusions                                                                                                                                                                     | 102 |

| Chapitre IV :                                                                                                                                                                       |     |

| Circuits de lecture colonne à faible bruit spatial fixe pour le capteur APS                                                                                                         | 107 |

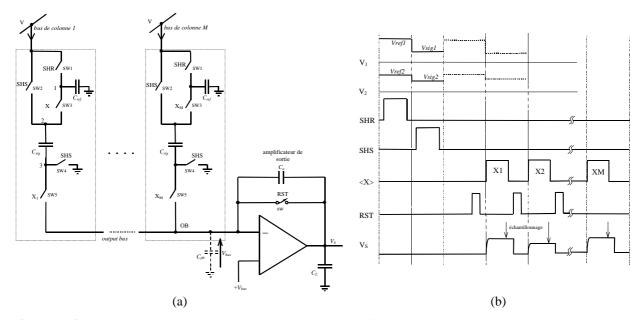

| 4.1 Introduction                                                                                                                                                                    | 107 |

| 4.2 Présentation du circuit de lecture du signal des colonnes                                                                                                                       | 109 |

| 4.3 L'amplificateur opérationnel                                                                                                                                                    | 111 |

| 4.4 Circuit de test                                                                                                                                                                 | 113 |

| 4.5 Effets des non-idéalités des composants utilisés                                                                                                                                | 116 |

| 4.5.1 Capacités parasites                                                                                                                                                           | 117 |

| 4.5.1.1 Capacité parasite du bus de sortie                                                                                                                                          | 117 |

| 4.5.1.2 Capacités parasites associées aux armatures des capacités réalisées en CMOS                                                                                                 | 117 |

| 4.5.1.3 Analyse de la fonction de transfert du circuit en présence des capacités parasites                                                                                          | 117 |

| 4.5.1.4 Réduction des effets des capacités parasites                                                                                                                                | 121 |

| 4.5.2 Problèmes liés aux interrupteurs                                                                                                                                              | 123 |

| 4.5.2.1 L'injection de charge ("charge injection")                                                                                                                                  | 123 |

| 4.5.2.2 L'injection d'horloge ("clock feedthrough")                                                                                                                                 | 124 |

| 4.5.2.3 Bruit kT/C                                                                                                                                                                  | 124 |

| 4.5.2.4 Réduction des effets non-idéaux des interrupteurs                                                                                                                           | 125 |

| 4.5.3 Bruit de l'OTA                                                                                                                                                                | 126 |

| 4.6 Conclusions                                                                                                                                                                     | 128 |

| Chapitre V :                                                                                                                                                                        |     |

| Conclusions et perspectives                                                                                                                                                         | 131 |

| Annexe - 1                                                                                                                                                                          |     |

| A1.1 Bruit du suiveur NMOS du pixel échantillonné sur la capacité $C_S$ ( $C_{ref}$ ou $C_{sig}$ )                                                                                  | 139 |

| A1.2 Gain DC des suiveurs                                                                                                                                                           | 140 |

| Annexe - 2                                                                                                                                                                          |     |

| A2.1 Calcul des effets du gain statique fini et de la tension de décalage de l'OTA sur la tension de sortie de l'amplificateur de tension élémentaire                               | 141 |

| A2.2. Calcul des effets du gain statique fini et de la tension de décalage de l'OTA sur la tension de sortie de l'ampli. de tension à c.c. à compensation de la tension de décalage | 143 |

# Introduction

Les capteurs d'images à transfert de charges (CCDs) inventés au début des années 70 ont quasiment remplacés les tubes à vides, les vidicons par exemple, dans tous les domaines de l'imagerie visible, aussi bien pour les applications grand public que pour l'imagerie scientifique.

Au début des années 90, un nouveau type de capteur d'images à l'état solide, appelé APS (active pixel sensor ou capteur d'images à pixels actifs) a été étudié par plusieurs laboratoires au Japon et aux Etats-Unis, et notamment par le Jet Propulsion Laboratory (JPL) en Californie [1]. Ce capteur, réalisé sur les technologies CMOS, offre plusieurs avantages par rapport aux CCDs, à savoir : faible consommation en puissance, coût de fabrication réduit, possibilité d'intégrer des circuit de traitement sur la même puce que le capteur (d'où miniaturisation du système), possibilité d'effectuer des lectures rapides, etc.

L'introduction de l'APS a également stimulé les recherches sur tous les types d'imageurs CMOS, dont certains existaient bien avant les CCDs. Ils sont sur le point de remplacer les CCDs dans plusieurs domaines. Parmi les applications diversifiées dont le nombre ne cesse d'augmenter, on peut citer par exemple le domaine grand public (caméscopes, multimédia, photographie numérique, jouets, caméras intégrées sur divers appareils portables...), le secteur d'automobile (anti-collision, guidage...), le domaine industriel (identification, contrôle industriel...), les applications nécessitant des vitesses de lectures très élevées (balistique, sport, "crash-tests" pour les automobiles, analyse d'explosion, etc.), et également le domaine scientifique et militaire (senseurs stellaires utilisés pour positionner les satellites, imagerie médicale, guidage, etc.) [2]-[4]. Des caméras numériques commerciales réalisées sur une seule puce ont été déjà présentées par plusieurs sociétés, avec des résolutions et des vitesses de lectures dépendant des applications, allant de quelques dizaines à quelques centaines d'images par seconde [5]-[10].

Aujourd'hui les recherches dans les imageurs CMOS sont orientées vers l'amélioration des performances électro-optiques du capteur (réduction du bruit temporel, du bruit spatial, et du courant d'obscurité,

augmentation de l'efficacité de détection, etc...), ainsi que vers l'intégration des circuits de traitement de plus performants sur la même puce que le capteur.

En France, le groupe de recherche C.I.M.I. (Conception d'Imageurs Matriciels Intégrés) de SUPAERO (Ecole Nationale Supérieure de l'Aéronautique et de l'Espace) a démarré des recherches sur le concept APS en 1995, et s'intéresse plus particulièrement aux applications spatiales en collaboration avec des industriels et des grands organismes scientifico-industriels.

C'est dans ce contexte qu'une partie importante de cette thèse a été consacrée à l'étude et la réduction du bruit temporel du capteur APS, qui est l'un des problèmes limitant les performances à faible flux du capteur. Le deuxième axe porte sur la conception de circuits analogiques de lecture et de traitement de signal, intégrés sur la même puce que le capteur.

Dans ce manuscrit, le travail effectué durant la thèse n'est pas présenté dans l'ordre chronologique. Les chapitres sont assez indépendants les uns des autres, et organisés de telle sorte que le lecteur s'intéressant à l'un des sujets présenté dans un chapitre ne soit pas obligé de lire tout le reste du manuscrit. Afin de faciliter leur accès, les références bibliographiques sont placées à la fin de chaque chapitre.

Le capteur APS et son fonctionnement, ainsi que les notions de base sur le bruit temporel et spatial, sont présentés dans le Chapitre I. Les autres chapitres font souvent référence à ce dernier.

Les travaux de cette thèse ont débuté par la réalisation de trois circuits de traitement intégrés pour la chaîne de lecture de l'APS. Ils assurent l'extraction et l'amplification du signal utile issu du capteur, proportionnel au flux lumineux incident, ainsi que la correction du bruit spatial fixe de colonnes. Ces circuits seront présentés dans le Chapitre III. Puis une étude théorique et la caractérisation expérimentale des réponses non-stationnaires en bruit blanc et en bruit basse fréquence de ces circuits ont été effectuées, qui sont également présentées dans le même chapitre. Les calculs de réponses en bruit de ce chapitre sont basés sur la résolution numérique des équations stochastiques différentielles. Pour le bruit en  $1/f^{\alpha}$ , nous avons appliqué le modèle diffusif développé dans les références [11][12].

Ensuite on s'est intéressé à la modélisation, présentée dans le Chapitre II, du bruit temporel généré par la chaîne de lecture. Les méthodes de calculs de bruit utilisées dans ce chapitre sont basées sur les densités spectrales de bruit et les fonctions de transfert. Les résultats théoriques et expérimentaux nous ont permis de réduire le bruit temporel, en optimisant les dimensions des composants, sans modifier la technologie CMOS standard utilisée.

Les recherches conduites en parallèle à ces études de bruit nous ont conduits à un nouveau circuit de lecture du signal des colonnes pour le capteur APS, qui présente certains avantages par rapport au circuit de lecture classique. Ce circuit est présenté dans le Chapitre IV. Les problèmes rencontrés sur un premier circuit de prototype et des améliorations possibles à apporter dans le prolongement de cette thèse sont également discutés.

Le dernier chapitre, Chapitre V, plus court, donne les perspectives dans le futur proche, ainsi que les difficultés à surmonter en termes de bruit et de dynamique pour réaliser des capteurs APS performants avec des circuits de traitement analogiques intégrés, sur les technologies CMOS submicroniques fonctionnant sous des tensions d'alimentation inférieures à 1V.

### Bibliographie:

- [1] E.R. Fossum, "Active pixel sensors: Are CCD's dinosaurs?," in *Charge Coupled Devices and Solid-State Optical Sensors III*, *Proceedings of SPIE*, vol. 1900, 1993, pp. 1-13.

- [2] E.R. Fossum, "Assessment of image sensor technology for future NASA missions," in *Charge-Coupled Devices and Solid State Optical Sensors IV, Proceedings of SPIE*, vol. 2172, 1994, pp. 38-53.

- [3] Photobit Co., [Online] http://www.photobit.com/.

- [4] M. Schanz *et al.*, "A high-dynamic-range CMOS image sensor for automotive applications," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 7, July 2000, pp. 932-938.

- [5] S.G. Smith *et al.*, "A single-chip CMOS 306×244-pixel NTSC video camera and a descendant coprocessor device," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, December 1998, pp. 2104-2111.

- [6] M.J. Loinaz *et al.*, "A 200-mW, 3.3-V, CMOS color camera IC producing 352x288 24-b video at 30 Frames/s", *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, December 1998, pp. 2092-2103.

- [7] S. Agwani et al., "A 1/3-inch VGA CMOS imaging system on a chip", Proc. 1999 IEEE Workshop on Charge Coupled-Devices and Advanced Image Sensors, Nagano, Japan, pp. 21-24.

- [8] B. Mansoorian *et al.*, "A 250mW, 60 frames/s 1280x720 pixel 9b CMOS digital image sensor", in *1999 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Tech. Papers*, San Francisco, pp. 312-313.

- [9] A. Krymski *et al.*, "A high speed, 500 Frames/s, 1024x1024 CMOS active pixel sensor", in *1999 Symposium on VLSI Circuits Digest of Tech. Papers*, Kyoto, Japan, pp. 137-138.

- [10] N. Stevanovic *et al.*, "A CMOS image sensor for high-speed imaging", in 2000 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Tech. Papers, San Francisco, pp. 104-105.

- [11] F. Lavernhe and J. Solhusvik, "Fractional noises: Diffusive model for CCD imager band-pass acquisition chain," in *Fractional Differential Systems*, *ESAIM Proceedings*, vol. 5, December 1998 (Paris), pp. 119-130.

- [12] F. Lavernhe, G. Montseny and J. Audounet, "Markovian diffusive representation of  $1/f^{\alpha}$  noises and applications to fractional stochastic differential models," *IEEE Transactions on Signal Processing*, vol. 49, no. 2, February 2001, pp. 414-423 (to be published).

# Chapitre I

# Les Capteurs d'Images du CCD à l'APS : Aspects Généraux et Bruit

## 1.1 Le capteur CCD [1][2]

Le dispositif à transfert de charges ou capteur CCD (Charge Coupled Device) a été inventé en 1970 par W.S. Boyle et G.E. Smith dans les Laboratoires Bell [3]. Il est basé sur une capacité MOS (Métal-Oxyde-Semiconducteur) dont la grille est polarisée (voir Figure I.1). Cette tension de polarisation provoque un dépeuplement des trous P sous la grille de la capacité MOS. La lumière traverse l'électrode de la capacité MOS et une génération d'une paire électron-trou se produit. Sous l'effet du champ, le photoélectron est attiré sous la grille et le trou repoussé dans le volume du substrat.

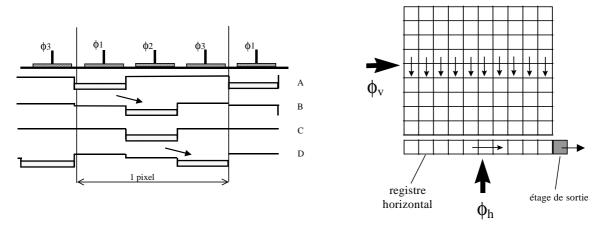

Chaque pixel est constitué d'une ou plusieurs grilles et les photoélectrons une fois collectés sont transférés verticalement d'une ligne à une autre à l'aide de plusieurs phases d'horloges (de 2 à 6 phases  $\phi_V$ ) vers un registre horizontal. Ensuite, ces charges sont transférées horizontalement par des phases d'horloge  $\phi_H$  vers l'étage de sortie, dont le but est de convertir les photoélectrons en une tension.

Figure I.1: (a) CCD avec transfert de charges à trois phases, (b) Exemple de lecture d'un CCD pleine trame.

Deux types d'étages de sortie sont principalement utilisés pour les capteurs CCDs, l'étage à grille flottante et l'étage à diffusion flottante [4]. L'étage à grille flottante permet de lire le signal plusieurs fois sans

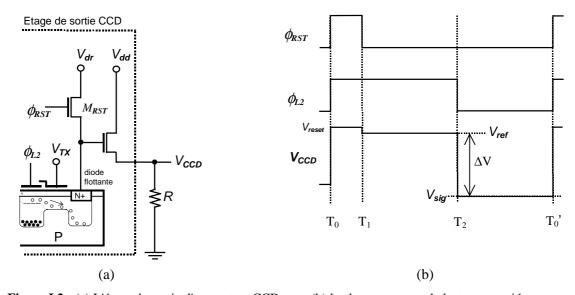

détruire le signal (lecture non destructive). Ainsi, on peut sommer les échantillons jusqu'à un niveau où le rapport signal/bruit est suffisant pour pouvoir utiliser l'image. Cette méthode permet donc d'obtenir une très bonne sensibilité. L'inconvénient est qu'il faut en général un grand nombre d'échantillons pour éliminer le bruit, ce qui mène à un temps de lecture relativement long. C'est pourquoi la plupart des CCDs utilisent la structure à diffusion flottante (ou diode flottante) qui est illustrée dans la Figure I.2.

Ce type d'étage de sortie est dit à diffusion flottante (ou diode flottante) car le potentiel de la diode (N+/P) est flottant lorsque le transistor de reset  $M_{RST}$  n'est pas activé (c'est-à-dire lorsque  $\phi_{RST}$  est au niveau bas). La capacité de transition (ou dépeuplement) de la diode, préchargée à un niveau de référence  $V_{dr}$  par l'intermédiaire de  $M_{RST}$ , reçoit, par injection, des charges électriques en provenance d'un pixel du CCD. Un étage suiveur, ayant un gain voisin de l'unité, permet de récupérer ("lire") le signal aux bornes de la diode flottante sans la perturber.

Le fonctionnement de cet étage de sortie est le suivant (cf. chronogramme, Figure I.2) :

A l'instant  $T_0$ :  $\phi_{RST} = \text{niveau haut } => \text{initialisation de la diode de sortie, c'est-à-dire pré-chargement}$

de la capacité à la tension  $V_{\text{dr}}$  donnant en sortie un niveau  $V_{\text{reset}}$  .

A l'instant  $T_1$ :  $\phi_{RST}$  = niveau bas => le transistor  $M_{RST}$  est bloqué et on garde le niveau de référence (le

décalage est dû au couplage capacitif entre l'entrée et la sortie du transistor  $M_{RST}$ ).

A l'instant  $T_2$ :  $\phi_{L2}$  = niveau bas => injection de charges dans la diode de sortie, ce qui induit une

diminution de la tension de sortie ( $\Delta V = V_{ref} - V_{sig}$ ).

A l'instant T<sub>0</sub>': le phénomène recommence pour lire le pixel suivant.

En conclusion, le signal à la sortie d'un CCD comprend 3 paliers par période d'un pixel : (i) le palier de reset, (ii) le palier de référence et (iii) le palier de signal. Le signal utile, proportionnel au flux reçu par le capteur, est représenté par la différence  $\Delta V$  entre le niveau de référence et le niveau de signal.

Le but de la chaîne d'acquisition est donc de mesurer  $\Delta V$  le plus précisément possible, malgré le bruit qui se superpose au signal. Une technique de mesure différentielle portant le nom de **double échantillonnage corrélé** (ou Correlated Double Sampling – **CDS**) [5] permet d'éliminer le bruit thermique généré par le transistor  $M_{RST}$  lors de la phase de reset et stocké sur la capacité équivalente à la diode flottante. Pour une tension  $V_d$  appliquée en inverse aux bornes d'une diode N+/P, la valeur de cette capacité est définie cidessous [6] :

$$C_d(V_d) = \sqrt{\frac{q \cdot \varepsilon_{si} \cdot N_A}{2 \cdot \left(V_{bi} + V_d - \frac{2kT}{q}\right)}} \cdot A_d \tag{1.1}$$

$C_d$ : capacité du détecteur photodiode polarisé en inverse (F),

q : charge élémentaire (1,6 x  $10^{-19}$  C),  $\varepsilon_{vi}$  : permittivité du silicium ( $10^{-12}$  F/cm),

$N_A$ : concentration des dopants P (atomes/cm<sup>3</sup>),  $V_{bi}$ : tension interne ("built-in") de la diode (V),  $V_d$ : tension inverse aux bornes de la diode (V),

$A_d$ : surface de la diode (cm<sup>2</sup>).

Cette formule montre que la valeur de cette capacité est proportionnelle à la surface et, de plus, varie avec  $V_d$ .

Figure I.2 : (a) L'étage de sortie d'un capteur CCD avec (b) le chronogramme de lecture associé.

Le capteur CCD a atteint aujourd'hui sa maturité et est utilisé dans toutes les applications d'imagerie, aussi bien dans le domaine grand public que scientifique, comme par exemple, l'astronomie, l'imagerie médicale ou la photographie d'art numérique. On peut trouver dans le commerce des CCDs très performants, avec un nombre de pixels allant jusqu'à 7Kx9K (soit 63 millions de pixels), un rendement quantique de 90%, un bruit de lecture inférieur à 1 électron, et des courants d'obscurité de l'ordre de 5pA/cm². Néanmoins, l'usage d'une technologie spécifique au CCD augmente considérablement le coût de fabrication de ce capteur et réduit les possibilités d'intégration des fonctions de traitement.

## 1.2 Le capteur APS

#### 1.2.1 Introduction

Les capteurs PPS (Passive Pixel Sensor ou capteur d'images à pixels passifs, appelé aussi "capteur d'images MOS-XY" [4]) existaient même avant l'invention du CCD [7], cependant les performances de ces capteurs sont loin d'être satisfaisantes pour les applications faible flux, en raison principalement du niveau de bruit très élevé (typiquement supérieur à 250 électrons) [8]. De nos jours les capteurs PPS sont toujours utilisés dans les applications grand public, et il existe toujours des travaux effectués sur ce type de capteur, en raison de sa simplicité et son taux de remplissage dans le pixel élevé [9][10].

Le progrès de la microélectronique de ces dernières années, a ouvert la possibilité de réaliser de nouvelles structures photosensibles sur des technologie CMOS qui apportent certains avantages par rapport aux CCDs. L'un de ces capteurs est le capteur APS (Active Pixel Sensor ou capteur d'image à pixels actifs) CMOS, introduit par plusieurs laboratoires au début des années 90 [11], et qui est très prometteur aussi bien pour l'imagerie faible flux que pour les applications grand public [12][13].

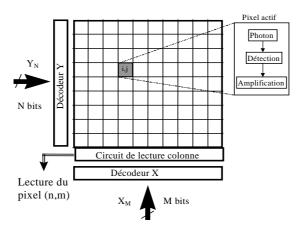

Le concept APS consiste à associer à chaque pixel du détecteur photosensible, des transistors actifs amplifiant le signal à proximité du capteur élémentaire, afin d'éliminer les problèmes dus au transfert des charges rencontrés dans les matrices CCD classiques (voir Figure I.3). Il permet aussi, à l'aide de transistors de sélection, d'adresser directement chaque pixel.

Le capteur d'image APS présente, par rapport aux capteurs CCDs, plusieurs avantages :

- Accès aléatoire et fenêtrage possible,

- Vitesse de lecture élevée,

- Procédé de fabrication CMOS standard à très grande diffusion (technologie des microprocesseurs et des mémoires),

- La lecture de toute une colonne n'est pas inhibée par un pixel défectueux,

- Possibilité d'intégrer l'électronique de séquencement et de traitement sur la même puce que le capteur,

- Faible consommation de puissance (20 50 mW) et tension d'alimentation standard (5V 1.2V),

- Possibilité de profiter de l'augmentation régulière de la finesse de la technologie pour réaliser des matrices de grande taille.

La réalisation de capteurs d'images "intelligents" (ou "caméra sur une seule puce") comprenant des photodétecteurs, des amplificateurs, convertisseur analogique-numérique, séquenceur et des circuits de traitement sur la même puce que le capteur, est donc possible [12], [14]-[16].

Figure I.3: Structure de base d'un capteur d'images à pixels actifs où chaque pixel est pourvu d'une partie photosensible et de son amplificateur.

### 1.2.2 Architecture générale d'une matrice APS

L'organisation et le fonctionnement de la matrice APS avec la chaîne d'acquisition associée seront expliqués brièvement.

#### 1.2.2.1 Le pixel

Dans cette partie seront présentés la structure et le fonctionnement des pixels utilisés actuellement dans les capteurs APS. Il existe deux types de structure principales pour la partie photosensible du capteur : la photodiode et le photoMOS. Ce sont les deux structures qui sont étudiées au Laboratoire CIMI (Conception d'Imageurs Matriciels Intégrés), à SUPAERO [17]-[21].

## A. Pixel Photodiode

#### i) Principe de base

La photodiode est une jonction P/N polarisée en inverse, qui génère un courant lorsqu'elle est éclairée par un flux photonique. La technologie CMOS permet de concevoir des photodiodes simples basées sur une structure N+/P, dont la région P correspond au substrat et la région N+ est fabriquée de la même manière qu'un drain ou une source de transistor NMOS.

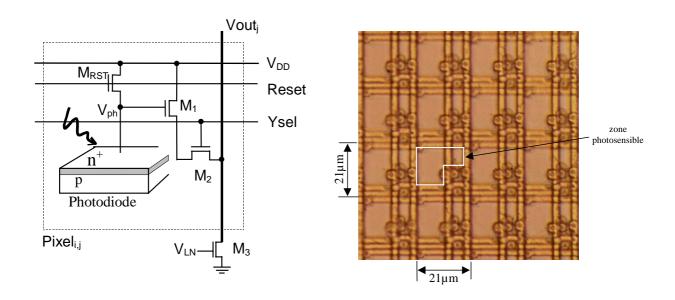

**Figure I.4:** (a) Schéma d'un pixel APS à base de photodiode, (b) Microphotographie d'un groupe de 4x4 pixels photodiodes réalisé sur une technologie *Alcatel Microelectronics* CMOS 0.7μm.

#### ii) Structure photodiode dans le pixel

La Figure I.4 montre la structure d'un pixel à photodiode. Ce pixel comporte une photodiode et 3 transistors.  $M_{RST}$  est utilisé pour initialiser la photodiode en début d'intégration. Les transistors  $M_1$ - $M_3$  forment un suiveur dont l'objectif est d'amplifier la tension de la photodiode et de l'acheminer via un bus vertical vers les circuits analogiques de traitement. L'avantage apporté par ce suiveur est la sortie à basse impédance du signal de la photodiode. La polarisation des transistors  $M_1$  et  $M_2$  est effectuée pour toute une colonne de pixel par un transistor de charge  $M_3$ , placé en bas de chaque colonne. Afin d'éviter le mélange des signaux sur le bus analogique colonne, le transistor  $M_2$  effectue la sélection du pixel de la ligne à lire.

#### iii) Fonctionnement

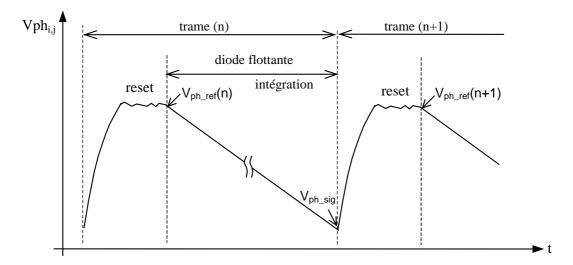

Le chronogramme du pixel peut se résumer ainsi (Figure I.5) : au début de l'intégration, le transistor  $M_{RST}$  est mis en position fermé pour initialiser la photodiode, ensuite ce transistor est relâché et la mesure du niveau de reset est effectuée ( $V_{ref}$ ), l'intégration fait chuter la tension de la diode et en fin d'intégration le

niveau de signal ( $V_{sig}$ ) est mesuré. La différence de ces deux signaux donne une tension proportionnelle à l'éclairement.

Figure I.5: Allure de la tension sur la photodiode du pixel de la figure I.4.

Cependant, dans le cas de l'intégration d'un pixel photodiode dans une matrice APS, le CDS ne peut pas être réalisé aisément. Cela tient au fait que la photodiode sert à la fois de photosite et de point de lecture du signal et qu'électriquement la diode n'est pas isolée du lieu où sont collectés les photons. Pour réaliser le CDS, il faudrait réussir à mémoriser en début d'exposition pour chaque pixel la valeur analogique de  $V_{ref}$ . Une solution consistant à numériser les signaux  $V_{ref}$  (CDS numérique), de toute la matrice est possible, mais reste très lourde à mettre en œuvre, un tel dispositif étant difficilement envisageable à cause de la complexité du système et du coût supplémentaire associé à la surface nécessaire pour une éventuelle intégration sur la puce.

D'un point de vue plus pratique, on réalise un double échantillonnage (non corrélé!) qui consiste à lire successivement le niveau de signal résultant de l'intégration de la trame (n), puis après "reset" du pixel, le niveau de référence de la trame suivante. Ce type de lecture permet de s'affranchir des différences de tensions de seuil de chaque pixel. Malheureusement, le bruit thermique généré par le transistor M<sub>RST</sub> n'est pas éliminé.

#### **B. Pixel PhotoMOS**

#### i) Principe de base

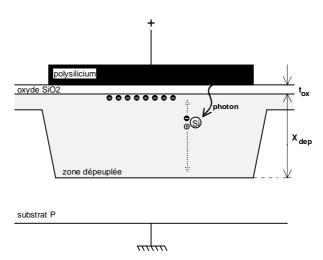

Alors que la photodiode utilise une jonction P/N, permettant une conversion directe des charges en tension, le détecteur photoMOS est basé sur une structure MOS ou jonction par effet de champ. L'application d'une tension positive provoque initialement un régime de dépeuplement profond, hors de l'équilibre thermodynamique (Figure I.6).

La zone de charge d'espace sous la grille constitue un puits de potentiel, capable de collecter et de retenir des charges photoniques (électrons). La structure consiste en un substrat de silicium dopé P, une couche d'oxyde mince (SiO<sub>2</sub>) et une grille en polysilicium (c'est-à-dire du silicium polycristallin fortement dopé au phosphore et rendu très conducteur).

Figure I.6 : Structure d'un détecteur photoMOS en dépeuplement profond.

Le même type de structure est utilisé dans les capteurs CCDs, car la structure photoMOS est capable non seulement de détecter et stocker des charges mais également de les transférer latéralement d'une capacité MOS à une autre située à une distance très proche en appliquant une séquence de polarisations appropriées sur les grilles comme pour un CCD.

La technologie de fabrication CMOS produit des structures de grilles de transistors NMOS complètement assimilables à une structure photoMOS. Autrement dit, le détecteur photoMOS est réalisé comme une grille NMOS de grande surface.

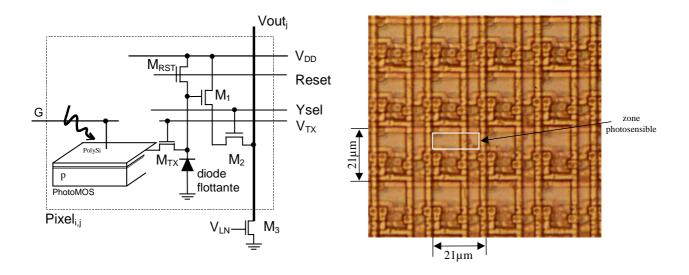

#### ii) Structure photoMOS dans le pixel

La réalisation dans le pixel de la structure photoMOS est illustrée Figure I.7. Une photo-grille définit la zone de collection des charges et les transistors  $M_{RST}$  et  $M_1$ - $M_3$  ont respectivement les mêmes fonctions que ceux illustrés dans le pixel photodiode. La source du transistor  $M_{TX}$ , commune avec celle du transistor  $M_{RST}$ , constitue la diode de lecture, élément de conversion charge-tension.

Le nombre de lignes de commandes du pixel est plus important par rapport au pixel photodiode, et le taux de remplissage dans le pixel est réduit.

**Figure I.7 :** (a) Schéma électrique d'un pixel APS photoMOS, (b) Microphotographie d'un groupe de 4x4 pixels photoMOS réalisé sur une technologie *Alcatel Microelectronics* CMOS 0.7μm.

#### iii) Fonctionnement

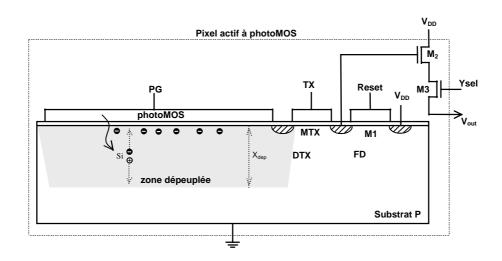

Une coupe longitudinale d'un pixel actif photoMOS sur substrat P pendant la phase d'intégration des charges est illustrée Figure I.8 .

La commande PG est portée au potentiel positif  $V_{DD}$ , permettant la création d'une zone dépeuplée de profondeur  $X_{dep}$ , les photons traversent la grille du photoMOS et créent des paires électrons trous dans le

volume. Sous l'effet du champ électrique, les trous sont repoussés dans le substrat et les électrons s'accumulent en surface sous la grille du photoMOS. Le rôle du transistor  $M_{TX}$  est d'isoler ces électrons de la diode de lecture FD. Le potentiel de TX est généralement fixé autour de 2V.

Figure I.8: Coupe d'un pixel photoMOS pendant l'intégration des charges

Une fois l'intégration terminée, la diode de lecture est rendue flottante en désactivant le transistor de reset  $M_{RST}$  par un signal numérique, le niveau de référence est mesuré et les charges sont transférées sur FD en établissant PG à 0V. Les charges traversent alors  $M_{TX}$  et vont décharger la diode de lecture, produisant un autre niveau de tension. La différence des deux signaux produit une chute de tension  $\Delta V$  sur  $V_{out}$  définie par :

$$\Delta V = N_e \frac{qA_1}{C_{fd}} = N_e C v f \tag{1.2}$$

$\Delta V$  : différence entre la valeur de référence et la valeur du signal à la sortie du pixel (V),

$N_e$ : nombre d'électrons photoniques accumulés dans le photoMOS,

$A_1$ : gain DC en tension du suiveur dans le pixel ( $\approx 0.8$ ),

$C_{fd}$  : capacité de la diode de lecture (F), Cvf : facteur de conversion (V/électron).

Le facteur de conversion *Cvf* est une donnée très importante, il donne la tension produite par un photoélectron capté par le pixel, et détermine la sensibilité.

Le pixel photoMOS présente l'avantage d'avoir un niveau de bruit de lecture très faible, par rapport à la photodiode. En effet, avec ce pixel, la technique CDS est réalisable et le bruit thermique généré par le transistor  $M_{RST}$  et échantillonné sur la diode de lecture est éliminé. De plus,  $C_{fd}$  pouvant être rendu très faible (quelques fF), des valeurs élevées de facteurs de conversion peuvent être atteintes (typiquement 10 à  $20 \,\mu\text{V/e}^-$ ). La relation (1.2) est valable également pour les pixels de type photodiode, mais dans ce cas,  $C_{fd}$  représente la capacité de la photodiode (plusieurs dizaines de fF) ce qui conduit à des facteurs de conversion souvent inférieurs à  $1\mu\text{V/e}^-$ .

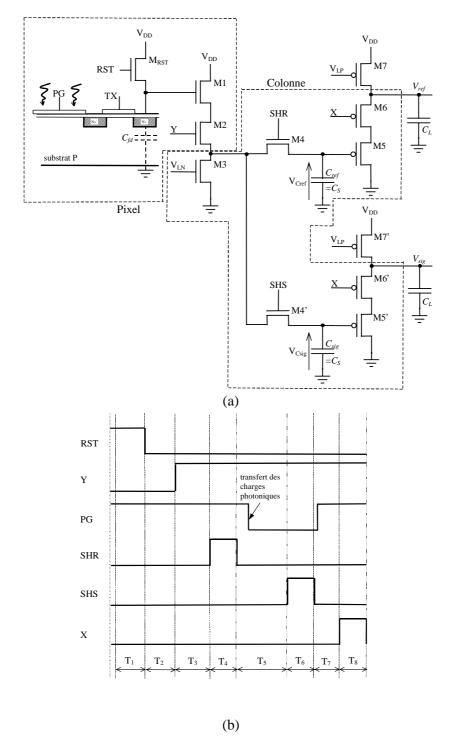

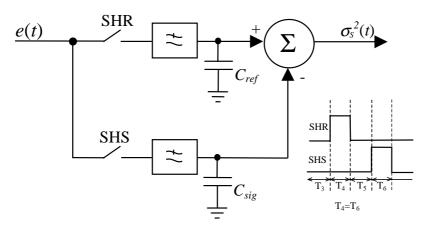

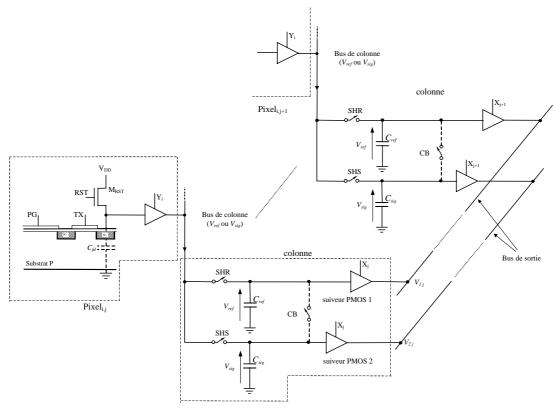

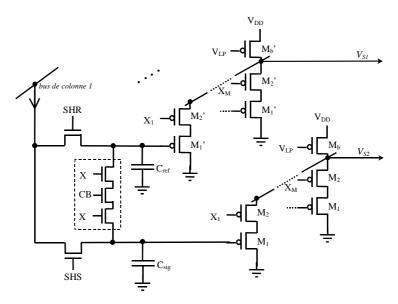

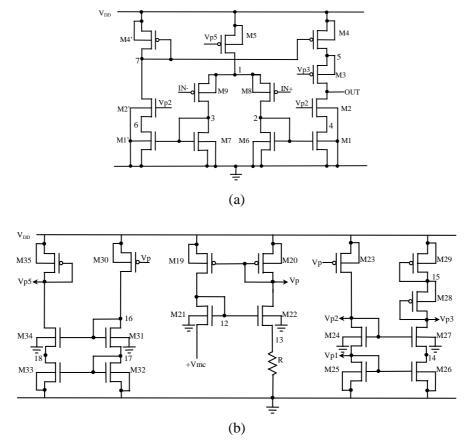

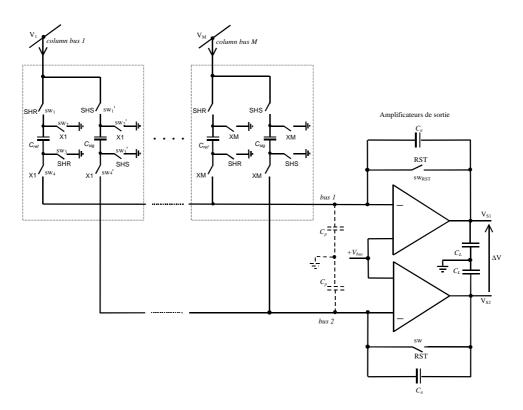

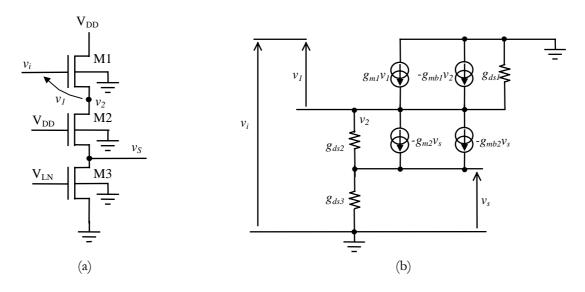

### 1.2.2.2 Circuits de lecture colonne

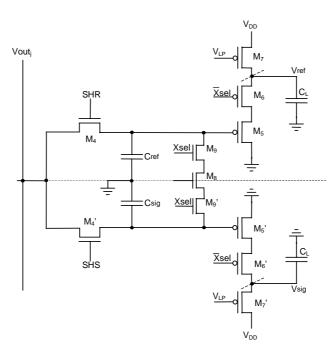

Le circuit de lecture du signal des colonnes utilisé actuellement dans la plupart des APS (Figure I.9) a été proposé dans la référence [13]. C'est un circuit complètement symétrique, implanté dans chaque colonne de la matrice. Les transistors  $M_5$ - $M_7$  forment un suiveur PMOS. Le transistor  $M_7$  (et son symétrique  $M_7$ ') est une source de courant, il est unique pour toute la matrice, alors que  $M_5$  et  $M_6$  sont présents pour chaque colonne de la matrice APS. La tension  $V_{LP}$  fixe le courant de polarisation de ce suiveur.

**Figure I.9 :** Circuit de lecture CDS d'une colonne de la matrice APS (les transistors  $M_7$  et  $M_7$ ' sont à l'extérieur de la colonne et communs à toute la matrice).

Le suiveur NMOS, qui est utilisé dans les pixels, procure une tension qui est décalée vers le bas par rapport à la tension d'entrée. Lorsque la tension à l'entrée du suiveur venant de la diode flottante du pixel (Vin) varie entre 3 et 4 volts, le niveau correspondant en sortie (Vout<sub>j</sub>) varie entre 1 et 2 volts environ, ces valeurs sont stockées aux bornes de  $C_{ref}$  et  $C_{sig}$  de 1pF environ. Les tensions sur  $C_{ref}$  et  $C_{sig}$  sont donc amplifiées ("bufférisées") avec des suiveurs PMOS au lieu de NMOS parce que cette plage de tensions à l'entrée d'un éventuel suiveur NMOS produirait une réponse non linéaire.

Le signal  $Vout_j$  correspondant au pixel sélectionné de chaque colonne est échantillonné en deux temps : d'abord le palier de référence  $V_{ref}$  sur la capacité  $C_{ref}$  grâce à l'ouverture du transistor  $M_4$  par le signal global SHR, ensuite le palier de signal  $V_{sig}$  sur la capacité  $C_{sig}$  en activant le transistor  $M_4$ ' par le signal SHS.

Une fois cette opération réalisée, les adresses des colonnes (X) sont balayées pour que chaque colonne produise à la sortie de la puce la paire de signaux  $V_{sig}$  et  $V_{ref}$  de chaque pixel de la ligne lue. Les suiveurs PMOS séparent sur deux voies, les tensions  $V_{sig}$  et  $V_{ref}$  du signal Vout<sub>j</sub> qui contenaient séquentiellement le palier de signal et le palier de référence.

Cette chaîne permet le double échantillonnage corrélé. A l'extérieur de la puce, la différence des deux signaux  $V_{sig}$  et  $V_{ref}$  doit être réalisée et ainsi que la conversion analogique-numérique.

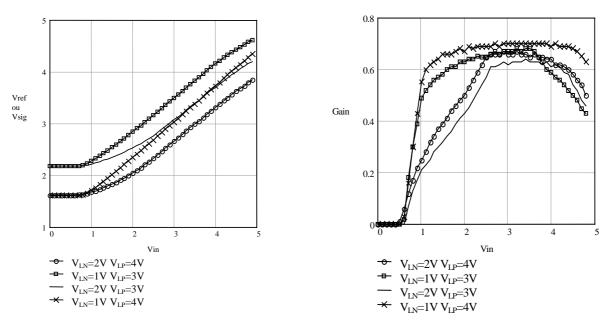

**Figure I.10:** (a) Simulation DC,  $V_{ref}$  en fonction de Vin pour plusieurs polarisations  $V_{LN}$  et  $V_{LP}$ , (b) Gains respectifs et variations en fonction de Vin.

Les Figure I.10a et Figure I.10b montrent respectivement les caractéristiques statiques par rapport à Vin et le gain statique à la sortie de l'ensemble de la chaîne de lecture du pixel ( $M_1$  à  $M_7$ ). La configuration qui produit le moins de variations de gain en fonction de Vin est celle où  $V_{LN}=1V$  et  $V_{LP}=4V$ . Dans le cas où  $V_{LP}=4V$ , le courant est 15 fois moins important que pour  $V_{LP}=3V$ . Cependant en terme de bande passante, il s'avère que la configuration avec un courant plus faible de polarisation sera bien moins rapide que celle à fort courant.

La configuration "normale" ( $V_{LN}$ =2V et  $V_{LP}$ =3V) montre qu'avec une charge de 6pF des fréquences pixels de l'ordre de 20Mpixels/sec. peuvent être aisément atteintes, mais au détriment de la linéarité. Si on décide de travailler avec  $V_{LN}$ =1V et  $V_{LP}$ =4V, pour atteindre cette fréquence, la charge devra être diminuée à 1pF ce qui est très difficile à réaliser en pratique, compte tenu des diverses capacités parasites (plots de la puce, etc..). Il est plus raisonnable de penser qu'avec cette polarisation et une charge de 6pF, une fréquence de 3-4 Mpixels/sec. pourra être atteinte. En conclusion, un compromis doit être trouvé en fonction de l'application.

Le rôle des transistors M<sub>8</sub>, M<sub>9</sub>, M<sub>9</sub>' et du signal CB illustrés Figure I.9 sera décrit dans la partie 1.4.3.

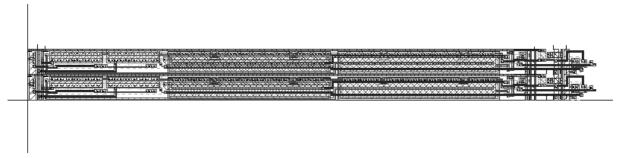

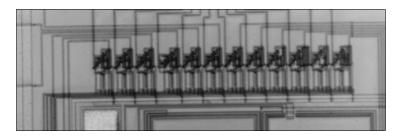

Le dessin de la chaîne de lecture de colonnes, réalisé sur le logiciel CADENCE, est illustré Figure I.11.

Figure I.11: Dessin de 2 circuits de lecture CDS aboutés.

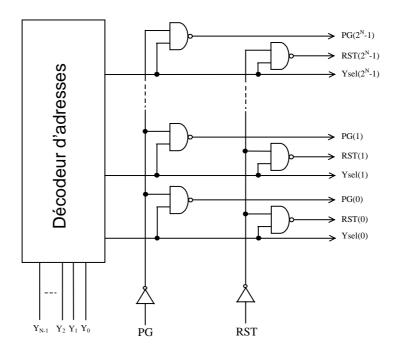

#### 1.2.2.3 Décodeurs d'adresses

Les décodeurs d'adresses acceptent N bits à l'entrée et sélectionnent ainsi une des (2<sup>N</sup>-1) colonnes ou des (2<sup>N</sup>-1) lignes (pour une matrice NxN). Le schéma électrique du décodeur d'adresses en Y est donné dans la Figure I.12 dans le cas du photoMOS. Ce circuit est valable pour les matrices à photoMOS. Le schéma est quasiment identique pour la matrice à photodiodes à l'exception du signal PG qui n'est pas utilisé. Les

lignes d'adresses  $Y_0$ - $Y_{N-1}$ , ainsi que les deux signaux de commande PG et RST, viennent de l'extérieur du circuit. Par conséquent, une seule ligne horizontale peut être adressée à la fois.

**Figure I.12 :** Schéma du décodeur d'adresses Y et de la partie logique associée aux signaux de commande (cas du photoMOS).

#### 1.2.2.4 Chronogramme de lecture de l'APS

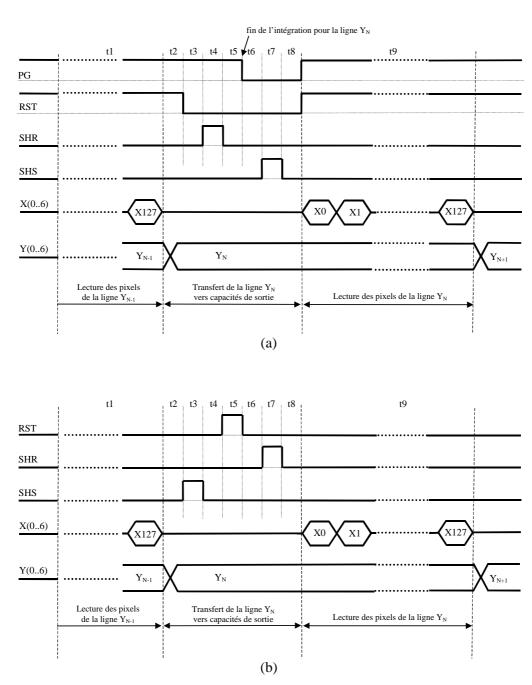

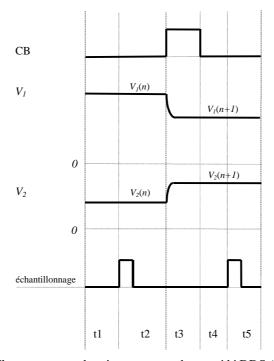

Le chronogramme de lecture diffère suivant le type de pixel. La Figure I.13a représente le chronogramme d'un APS photoMOS, et la Figure I.13b celui d'un APS photodiode.

Pour le photoMOS, lorsqu'une ligne est sélectionnée, toutes les lignes non adressées de la matrice se trouvent en phase d'intégration. La ligne sélectionnée continue également à intégrer jusqu'à ce que le signal PG passe à l'état bas. Dans le cas de la photodiode, les pixels intègrent tout le temps, sauf quand le signal RST est à l'état haut.

Lors de la lecture, l'information de la ligne sélectionnée  $Y_N$  est transférée vers les capacités  $C_{ref}$  et  $C_{sig}$  du circuit CDS. Pour le photoMOS, les valeurs des tensions  $V_{ref}$  sont échantillonnées en activant le signal SHR, après avoir bloqué les transistors de reset des pixels sélectionnés (par un état bas sur le RST externe). Ensuite, PG passe à l'état bas pour terminer l'intégration et permettre le transfert des charges vers la diode de lecture, et le signal SHS échantillonne l'ensemble des valeurs du niveau de signal  $V_{sig}$ .

Figure I.13: Chronogramme de lecture d'une matrice APS 128x128 (a) PhotoMOS, et (b) Photodiode.

Dans le cas de la photodiode, le signal  $V_{sig}$  est échantillonné en premier suivi du signal  $V_{ref}$ . Il est important de rappeler qu'il s'agit du  $V_{ref}$  correspondant à la trame suivante.

La dernière étape consiste à lire chaque pixel de la ligne transférée lors de la phase précédente. Il suffit pour cela de sélectionner chaque pixel en incrémentant le décodeur d'adresse X. Après la lecture du dernier pixel  $X_N$ , la ligne  $Y_{N+1}$  est adressée et le cycle recommence.

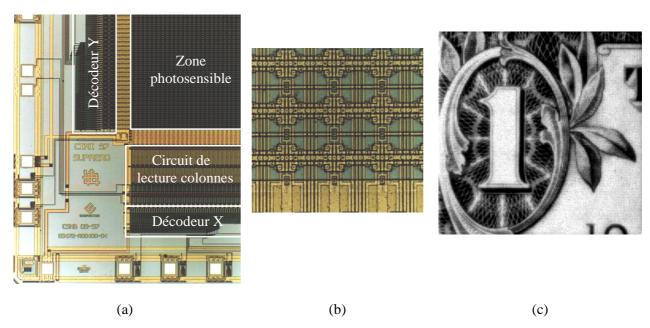

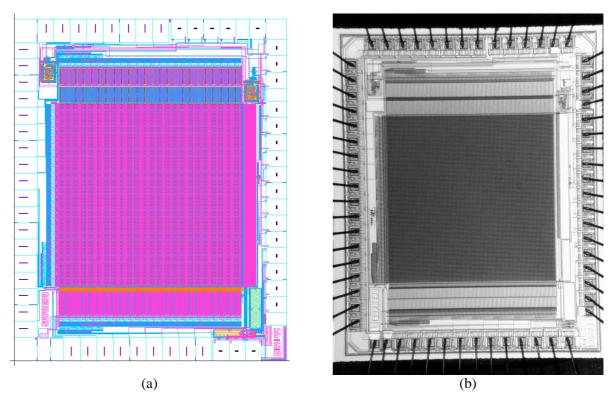

Les microphotographies de certaines parties d'une puce APS 256x256 pixels photoMOS, réalisée sur une technologie *Alcatel Microelectronics* CMOS 0.7µm, ainsi qu'une image produite avec ce capteur à 50kpixels/sec. sont représentées dans la Figure I.14 [19]. Dans la Figure I.14a, on remarque les décodeurs X et Y, les circuits de lecture colonnes, une partie de la zone photosensible, les plots d'entrées et de sorties de la puce. La Figure I.14b montre un groupe de 9x4 pixels. Le pas du pixel est 19µm.

**Figure I.14 :** (a) Photographie de la puce d'une matrice APS 256x256 pixels photoMOS réalisée sur une technologie *Alcatel Microelectronics* CMOS 0.7μm, (b) photographie de la partie photosensible de la même puce, (c) image produite par ce capteur à 50kpixels/sec.

## 1.3 Aspects généraux sur le bruit [22]-[27]

#### 1.3.1 Généralités

Dans la littérature des circuits et systèmes électroniques, le terme "bruit" est souvent utilisé pour désigner n'importe quel signal aléatoire non désiré mais présent dans le système.

Le niveau de signal le plus haut traitable par un système est déterminé par les caractéristiques de ce système, et le niveau le plus bas par le bruit.

Afin d'augmenter la dynamique à l'entrée d'un capteur d'images, par exemple celle d'un APS, deux méthodes sont possibles : la première consiste à réduire le niveau de bruit et améliorer la dynamique vers les faibles niveaux de flux et la seconde à augmenter le niveau de saturation à l'entrée et donc étendre la dynamique vers les forts niveaux d'éclairement. Etant donné que ce travail est orienté vers les applications spatiales, le plus souvent à faible flux lumineux, la méthode qui a été choisie est la première. Les méthodes pour augmenter le niveau de saturation sont décrites dans la référence [28].

Les sources de bruit peuvent être internes ou externes au système. Par exemple, le bruit thermique généré par les résistances ou composants actifs d'un circuit intégré constitue une source de bruit interne, et le bruit provenant de l'environnement à travers les interférences électromagnétiques ou électrostatiques une source de bruit externe. L'interférence électromagnétique peut aussi se produire entre divers composants appartenant au même système. Dans les circuits intégrés, par exemple, les parasites générés par les commutations des circuits numériques peuvent se propager grâce aux couplages électromagnétiques, aux pistes d'alimentations ou au substrat, en dégradant les performances des circuits analogiques qui se trouvent sur la même puce.

Le bruit interne, dit "bruit électrique" ou "bruit électronique", est un phénomène physique dû aux petites fluctuations du courant ou de la tension des composants utilisés dans les circuits intégrés.

Les perturbations dues aux sources de bruits externes peuvent aussi altérer le fonctionnement des circuits électroniques, dans certaines cas elles peuvent être même dominantes par rapport aux bruits internes. Néanmoins, elles peuvent être réduites considérablement en utilisant certaines méthodes de conception [30]-[32]:

- réalisation de dessins de puce soigneux,

- séparation des alimentations des circuits numériques et celles des circuits analogiques,

- isolation des parties analogiques sensibles du reste du système,

- utilisation de structures de circuit différentielles symétriques.

Ces considérations seront prises en compte lors de la réalisation des circuits présentés dans les chapitres suivants.

\_

<sup>&</sup>lt;sup>1</sup> Pour une application de ce type, voir par exemple la référence [29].

Par contre, les bruits électriques, comme le bruit thermique, le bruit de grenaille, ou le bruit de scintillement, sont inhérents au fonctionnement du composant et ne peuvent pas être éliminés en utilisant ces méthodes. Ces types de bruit déterminent donc le niveau de signal le plus bas traitable par le système, par exemple, le niveau d'éclairement le plus faible détectable par un capteur APS. C'est ce type de bruit qui sera étudié dans le Chapitre II.

Le bruit étant un phénomène totalement aléatoire, sa valeur efficace ou RMS (Root Mean Square) ainsi que sa moyenne peuvent être estimées et mesurées.

Pour effectuer une analyse du bruit dans les circuits électriques, la fluctuation du courant est décrite comme un signal aléatoire de puissance finie. Ce signal a une valeur quadratique moyenne  $\overline{i}^2$ , mesurée dans une bande de fréquence  $\Delta f$ . Par contre, sa valeur instantanée i(t) ne peut pas être estimée.

## 1.3.2 Bruit temporel

#### 1.3.2.1 Terminologie

En désignant par x(t) un signal aléatoire *réel* de puissance finie, centré en général [V ou A], et en notant

$S_r(f)$ : la densité spectrale de puissance de bruit [V<sup>2</sup>/Hz ou A<sup>2</sup>/Hz],

$\overline{x^2} = \sigma_x^2$ : la puissance du bruit ou variance [V² ou A²].

$\sigma_x$ : l'écart type du signal aléatoire (exprimé en  $V_{rms}$  ou  $A_{rms}$ ),

E[x(t)]: l'espérance mathématique ou moyenne du signal aléatoire [V ou A],

$R_{x}(\tau)$ : la fonction de corrélation ou autocorrelation du signal aléatoire stationnaire x(t),

$R_{yy}(\tau)$ : la fonction d'intercorrélation des signaux aléatoires stationnaires x(t) et y(t),

$x^*(t)$ : le complexe conjugué d'un signal aléatoire complexe x(t),

on peut établir les définitions suivantes :

Une **fonction aléatoire stationnaire** représente un phénomène aléatoire qui dépend du temps, mais dont les grandeurs statistiques n'en dépendent pas. Ainsi si x(t) est "stationnaire au sens strict", toutes ses

propriétés statistiques sont invariantes dans tout changement de l'origine du temps. De même, x(t) est "stationnaire au sens large" ou "faiblement stationnaire" (WSS – wide sense stationary), si ses moments du premier et deuxième ordre sont invariants dans tout changement de l'origine du temps.

La **densité spectrale de puissance bilatérale** (DSP)  $S_x(f)$  d'un signal aléatoire x(t) est la densité de répartition de la puissance  $\sigma_x^2$  du processus aléatoire sur l'axe des fréquences : c'est une fonction réelle, positive et paire.

La puissance  $\overline{x^2}$  du bruit est calculée par :

$$\overline{x^2} = \int_{-\infty}^{+\infty} S_x(f) df$$

$S_x(f)$  df est la puissance moyenne du signal dans la bande de fréquence df.

L'espérance mathématique E[x] (ou la moyenne) d'un signal aléatoire x(t) est définie de la moyenne d'ensemble suivante :

$$E[x(t)] = \int_{-\infty}^{+\infty} x(t) p(x) dx$$

où p(x) est la densité de probabilité de x. Dans le cas des processus ergodiques (donc stationnaires), cette moyenne d'ensemble peut être remplacée par une moyenne temporelle :

$$E[x] = \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{+T/2} x(t).dt$$

Ces expressions peuvent être généralisées aux moments d'ordre n.

La fonction d'autocorrélation est définie de la façon suivante :

$$R_x(\tau) = E[x(t). \ x^*(t - \tau)]$$

et la **fonction d'intercorrélation** des signaux aléatoires x(t) et y(t) par :

$$R_{xy}(\tau) = E[x(t), y^*(t - \tau)].$$

D'après le théorème de *Wiener-Kinchin*, si x(t) est un signal aléatoire faiblement stationnaire, sa fonction d'autocorrélation et sa densité spectrale forment une paire de transformées de Fourier :

$$\begin{cases} S_{x}(f) = \int_{-\infty}^{+\infty} R_{xx}(\tau) e^{-j2\pi f \tau} d\tau, & f \in \Re \\ R_{xx}(\tau) = \int_{-\infty}^{+\infty} S_{x}(f) e^{+j2\pi f \tau} df, & \tau \in \Re \end{cases}$$

où  $R_{xx}(\tau) = E[x(t), x^*(t - \tau)] = R_{xx}^*(-\tau)$ . On rappelle que la puissance totale est donnée par :

$$R_{xx}(0) = \overline{x^2} = \sigma_x^2$$

On montre de plus que  $S_x(f)$  peut être évaluée grâce à l'expression :

$$S_{x}(f) = \lim_{T \to \infty} E \left[ \frac{\left| X_{T}(f) \right|^{2}}{T} \right]$$

où  $X_T(f)$  est la transformée de Fourier du signal x(t) observé durant une durée T.

On utilise souvent en électronique la DSP unilatérale obtenue en prenant le double de la DSP bilatérale sur le domaine des fréquences réelles positives.

#### 1.3.2.2 Bruit thermique

Ce type de bruit est dû au mouvement aléatoire des porteurs de charges sous l'effet de la température. Il est associé à la résistance ou à la partie résistive d'un composant ; il est indépendant du courant et de la polarisation. Ce mouvement est similaire au *mouvement Brownien*<sup>2</sup> des particules. Il a été observé pour la première fois en électronique par J.B. Johnson aux *Bell Telephone Laboratories* en 1927, et sa densité spectrale a été calculée par H. Nyquist en 1928. C'est la raison pour laquelle il est connu sous les noms de "bruit Johnson" ou "bruit de Nyquist". La DSP unilatérale de courant du bruit thermique généré par une résistance *R* est donnée par :

$$S_{th,i}(f) = \frac{4kT}{R}$$

<sup>&</sup>lt;sup>2</sup> Robert Brown (1773-1858) est un botaniste écossais qui a observé pour la première fois le mouvement aléatoire des grains de pollen dans une solution.

où k est la constante de Boltzmann et T (en K) la température absolue<sup>3</sup>. La variance du bruit thermique est finie en raison de la bande passante limitée de tout système. La DSP étant constante, ce bruit est appelé bruit blanc.

Figure I.15 : Schéma équivalent de Norton en bruit d'une résistance.

## 1.3.2.3 Bruit de grenaille

Il est dû à la nature granulaire de l'électricité, c'est-à-dire à la non-uniformité du courant. Il intervient lorsque les porteurs franchissent une barrière de potentiel de façon aléatoire suivant une loi de Poisson. Il se manifeste dans les dispositifs à jonctions, tels que les diodes, les transistors bipolaires etc.

Ce bruit est directement proportionnel au courant passant à travers le composant. Dans la bande passante du système, si on néglige le temps de transit, la DSP unilatérale de ce bruit blanc est donnée par :

$$S_{gr,i}(f) = 2qI \quad (f \ge 0)$$

$$S_{th,i}(f) = \frac{4hf}{R\left(\exp\left(\frac{hf}{kT}\right) - 1\right)} \qquad f > 0$$

où h est la constante de Planck, f la fréquence. On remarque la DSP est fonction de la fréquence. Pour la plupart des systèmes électroniques, f << kT/h,  $(kT/h \approx 2.10^{10}T)$ . Donc,

$$\frac{hf}{\left(\exp\left(\frac{hf}{kT}\right) - 1\right)} \approx kT$$

et on obtient une DSP de bruit blanc :

$$S_{th,i}(f) = \frac{4kT}{R} \cdot$$

<sup>&</sup>lt;sup>3</sup> L'expression la plus générale du bruit thermique est donnée par :

où q est la charge électronique élémentaire et I l'intensité du courant continu passant à travers le composant.

### 1.3.2.4 Bruit en 1/f (bruit de scintillement ou "flicker noise")

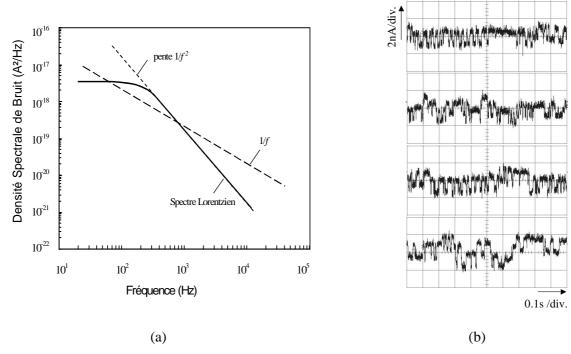

C'est un type de bruit ayant des propriétés uniques. La densité spectrale de ce bruit suit sensiblement une courbe en  $1/f^{\alpha}$ ,  $\alpha$  étant proche de 1. Il a été nommé bruit de scintillement après avoir été observé pour la première fois dans les tubes à vide. Dans la littérature, des noms tels que "bruit rose" (pour  $\alpha = 1$ ), "bruit en excès" ou "bruit basse fréquence" sont aussi souvent employés. Le bruit en  $1/f^2$  est appelé "bruit rouge": il correspond en fait à un bruit blanc intégré temporellement.

Une propriété importante du bruit de scintillement est son universalité. Ce type de bruit est non seulement observé dans les composants électroniques, mais dans des domaines très variés [33]-[38] : l'oscillation des cristaux de quartz, les données économiques (la bourse), le taux de la circulation routière, les données géophysiques, les courants dans les océans, le bruit sismique, le débit du Nil au cours des 2000 dernières années, le taux d'insuline, les variations du rythme cardiaque, les courants dans les fibres nerveuses, l'ADN, les fluctuations du potentiel de membrane dans un système biologique, l'activité solaire, les lumières émises par les naines blanches et les quasars, les oscillations de l'axe terrestre, la rotation de la terre, le son et la voix transmise par la radio, la musique, l'écoulement du sable dans un sablier, la distribution des nombre premiers, etc. Par exemple, pour la fréquence de la rotation de la terre,  $\alpha = 2$ .

Le bruit basse fréquence dans les transistors MOS sera présenté un peu plus en détail dans le chapitre II.

Etant donné que la densité spectrale du bruit en  $1/f^{\alpha}$  présente une singularité en f=0, le bruit a une puissance infinie si  $\alpha \ge 1$ . Donc, on devrait mesurer une valeur RMS infinie pour ce bruit qui n'est pas le cas en pratique. En effet, le fait d'observer ce bruit pendant une durée finie induit une fréquence de coupure basse. Donc la DSP moyenne de ce bruit dépend du temps et de la durée d'observation [39][33]. La fréquence de coupure haute est limitée par la bande passante du système. Ce sont les raisons pour lesquelles la valeur RMS mesurée en pratique est toujours finie, ce qui facilite aussi les calculs relatifs à ce bruit.

#### 1.4 Sources de bruit dans l'APS

Le signal de la sortie de l'APS comprend [40] :

- électrons générés par les photons incidents associés à un bruit de grenaille,

- électrons générés par le courant d'obscurité associés à un bruit de grenaille,

- bruit temporel de lecture,

- non-uniformités du courant d'obscurité,

- bruit spatial fixe des circuits de lectures,

Seuls les électrons générés par les photons incidents sont désirés, les autres sont des facteurs limitant la performance du capteur.

#### 1.4.1 Bruit de grenaille généré par les photons (bruit photonique)

C'est un phénomène physique qui ne peut pas être réduit. A fort éclairement, c'est la source de bruit dominante. Il est poissonien et sa variance est donnée par [41] :

$$\sigma_{photon}^2 = N_{photon} \tag{1.3}$$

$N_{photon}$  étant le nombre moyen de photons incidents.

#### 1.4.2 Courant d'obscurité et bruit de grenaille généré par le courant d'obscurité

Le courant d'obscurité est dû aux générations de charges thermiques dans le pixel. Il est mesuré en pA/cm². Il s'agit d'électrons qui se libèrent des atomes de silicium à cause de leur énergie thermique, et s'accumulent dans le pixel en se rajoutant aux électrons du signal photonique. Dans le cas du photoMOS, cette génération intervient majoritairement à l'interface Si-SiO<sub>2</sub> plutôt que dans le substrat lui même. Le taux de génération de ces charges thermiques varie beaucoup d'un pixel à l'autre et il en résulte une non-uniformité de courant thermique désigné par **DSNU** (Dark Signal Non Uniformity). La distribution spatiale en intensité de courant d'obscurité obéit la plupart du temps à une distribution gaussienne centrée

sur la moyenne du courant thermique, et les pixels ayant un courant plus élevé (donc en dehors de la distribution gaussienne) sont appelés des pixels chauds. Le courant d'obscurité est très dépendant de la température et il double tous les 5 à  $8^{\circ}$ C [40]. Une expression théorique donne la densité du courant d'obscurité J en fonction de la température T [4] :

$$J = A.T^{3/2}e^{-\frac{Vg.q}{2kT}}$$

où A est une constante dépendante des unités utilisées (en pA/cm²), Vg est la largeur de la bande interdite (ou tension de gap). Sa valeur est très dépendante du procédé de fabrication. A température ambiante, l'ordre de grandeur s'étend de 200 à 1500 pA/cm².

Le courant d'obscurité et les non-uniformités peuvent être corrigés, par contre le bruit de grenaille généré par le courant d'obscurité ne peut pas être corrigé [42]. Le seul moyen de corriger ce bruit et de réduire le courant d'obscurité. Le courant d'obscurité continue à être un problème majeur dans les imageurs CMOS, et jusqu'à présent, pour le réduire, seules des solutions modifiant la technologie CMOS standard utilisée ont été proposées [43].

#### 1.4.3 Bruit fixe (ou spatial) de la chaîne de lecture

Il exprime l'écart de réponse des éléments des circuits de lecture situés dans les différents pixels et les différentes colonnes d'une matrice APS. Il est dû principalement aux non-uniformités de certains paramètres des composants, surtout celles des transistors MOS utilisés : tensions de seuil, courants, transconductances, etc. La différence de tensions de seuil est la source de bruit fixe dominante [2]. En général, plus la distance entre deux transistors MOS est grande, plus la tension de seuil des deux transistors peut être différente. Typiquement, on peut avoir sur la même puce des variations de l'ordre d'une dizaine de millivolts [44][45].

Le bruit fixe total pour l'APS peut s'exprimer de la façon suivante [46] :

$$FPN_{i,j} = Y_j + X_{i,j} \tag{1.4}$$

où  $Y_j$  représente le bruit fixe de colonnes et  $X_{i,j}$  représente le bruit fixe de pixels. X et Y sont des variables aléatoires à moyenne nulle totalement décorrélés, obtenues en soustrayant aux mesures brutes la valeur

moyenne prise sur l'ensemble des signaux. L'estimation de la moyenne et de la variance pour une matrice de M lignes et N colonnes sont données par :

$$\overline{Y}_{j} = \frac{1}{N} \sum_{i=1}^{N} FPN_{i,j}$$

$$\tag{1.5}$$

$$\overline{X_{i,j}} = FPN_{i,j} - \overline{Y_j} \tag{1.6}$$

$$\overline{\sigma_Y^2} = \frac{1}{M - 1} \sum_{i=1}^M (\overline{Y}_i)^2$$

(1.7)

$$\overline{\sigma_X^2} = \frac{1}{M(N-1)} \sum_{i=1}^{N} \sum_{j=1}^{M} (\overline{X}_{i,j})^2$$

(1.8)

La technique de lecture CDS corrige efficacement le bruit spatial de pixel, et dans l'APS, le bruit fixe de colonne est dominant [13].

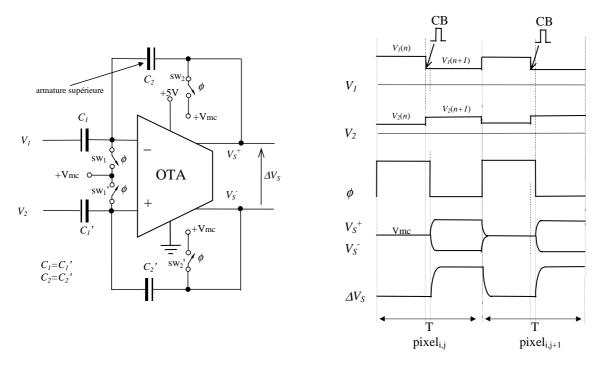

Dans la chaîne de lecture de l'APS (la Figure I.9), chaque colonne dispose de deux amplificateurs (suiveurs) séparés, dont la tension continue (DC) en sortie dépend fortement de la tension de seuil des transistors associés. Soit  $\Delta V_{pix}$  la différence des tensions aux bornes de  $C_{ref}$  et  $C_{sig}$ , et  $\Delta V_s$  (=  $V_{sig}$ - $V_{ref}$ ), la différence correspondante en sortie des deux suiveurs PMOS. Ainsi, on peut exprimer en première analyse la valeur de  $\Delta V_s$  de la manière suivante :

$$\Delta V_S = A_2 \Delta V_{pix} + \varepsilon$$

où  $A_2$  représente le gain DC des suiveurs PMOS, et  $\varepsilon$  la différence des tensions de repos de chacun des amplificateurs.

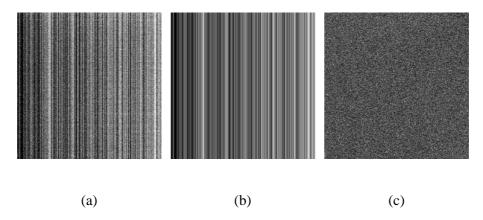

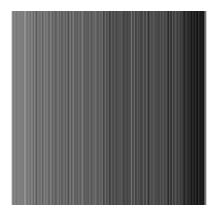

Le bruit fixe de colonne provient du fait que  $\varepsilon$  varie d'une colonne à une autre, ce qui se traduit sur l'image par l'apparition de rayures verticales pour une scène parfaitement homogène. La Figure I.16 montre la moyenne de 50 images obtenus dans l'obscurité avec un APS 256x256 pixels [20]. On remarque sur ces images le bruit fixe de pixel (0.34% ramené à la dynamique du capteur) et le bruit fixe de colonne (0.84% ramené à la dynamique du capteur).

Actuellement, afin de corriger le bruit fixe de colonne, la méthode d'échantillonnage par double différence <sup>4</sup> (ou **DDS** - Double Delta Sampling) est utilisée [13]. Le procédé DDS est effectué grâce aux

\_

<sup>&</sup>lt;sup>4</sup> On reviendra beaucoup plus en détail sur cette méthode dans le Chapitre III.

transistors  $M_8$ ,  $M_9$ ,  $M_9$ ' et le signal CB ("Crow Bar"), illustrés Figure I.9. Cette méthode consiste à mesurer la valeur de  $\varepsilon$  et à la soustraire à  $\Delta V_s$ . La lecture DDS se fait de la manière suivante. D'abord, la valeur de  $\Delta V_s$  est mesurée et stockée par la chaîne externe. Ensuite, les deux capacités  $C_{ref}$  et  $C_{sig}$  sont court-circuitées. Cela est assuré par le signal de commande CB qui est mis à l'état haut pour créer un court-circuit entre les capacités. Par conséquent,  $\Delta V_{pix}$  devient nul et à la sortie il ne reste uniquement que  $\varepsilon$  qui est échantillonné et soustrait à  $\Delta V_s$  par la chaîne externe.

L'inconvénient de cette méthode est qu'il faut effectuer deux échantillonnages par pixel au lieu d'un seul, ce qui augmente le temps de lecture ainsi que le bruit temporel apporté par ce nouvel échantillonnage.

**Figure I.16 :** Somme de 50 images obtenues dans l'obscurité avec un APS 256x256 pixels : (a) bruit fixe total, (b) bruit fixe de colonne, et (c) bruit fixe de pixel.

#### 1.4.4 Bruit temporel de lecture

Le bruit temporel de la chaîne de lecture est le bruit dominant à faible niveau d'éclairement et faible temps d'intégration, et constitue un paramètre d'importance majeure pour les applications à faible flux. Ce bruit sera analysé en détail dans le Chapitre II.

#### Bibliographie:

- [1] C. Cavadore, "Conception et caractérisation de capteurs d'images à pixels actifs CMOS-APS," Thèse de Doctorat, no. 242, SUPAERO, Toulouse, Juin 1998.

- [2] J. Solhusvik, "Etude et conception de capteurs d'images à pixels actifs et de l'électronique de traitement associée en vue d'applications faible flux," Thèse de Doctorat, no. 195, SUPAERO, Toulouse, Novembre 1996.

- [3] W.S. Boyle and G.E. Smith, "Charge-coupled semiconductor devices," *Bell System Technical Journal*, vol. 49, April 1970, pp. 587-593.

- [4] A.J.P. Theuwissen, *Solid-State Imaging with Charge-Coupled Devices*, Kluwer, Dordrecht, The Nederlands, 1995.

- [5] M.H. White, D.R. Lampe, F.C. Blaha, and I.A. Mack, "Characterization of surface channel CCD image arrays at low light levels," *IEEE Journal of Solid-State Circuits*, vol. SC-9, no. 1, February 1974, pp. 1-13.

- [6] S.M. Sze, *Physics of Semiconductor Devices*, Wiley, New York, 1981.

- [7] G.P. Weckler, "Operation of p-n junction photodetectors in photon flux integration mode," *IEEE Journal of Solid-State Circuits*, vol. SC-2, 1967, pp. 65-73.

- [8] C. Jansson, P. Ingelhag, C. Svensson, and R. Forchheimer, "An addressable 256x256 photodiode image sensor array with an 8-bit digital output," *Analog Integrated Circuits and Signal Processing*, vol. 4, 1993, pp. 37-49.

- [9] A. Simoni *et al.*, "256x256-pixel CMOS digital camera for computer vision with 32 algorithmic ADCs on board," *IEE Proceedings Circuits, Devices and Systems*, vol. 146, no. 4, August 1999, pp. 184-190.

- [10] I. Fujimori, C.C. Wang, and C.G. Sodini, "A 256x256 CMOS differential passive pixel imager with FPN reduction techniques," in 2000 IEEE Int. Solid-State Circuits Conference (ISSCC) Digest of Tech. Papers, San Francisco, pp. 106-107.

- [11] E.R. Fossum, "Active pixel sensors: Are CCD's dinosaurs?," in *Charge Coupled Devices and Solid-State Optical Sensors III, Proceedings of SPIE*, vol. 1900, 1993, pp. 1-13.

- [12] E.R. Fossum, "CMOS image sensors: Electronic camera-on-a-chip," *IEEE Transactions on Electron Devices*, vol. 44, no. 10, October 1997, pp. 1689-1698.

- [13] S.K. Mendis *et al.*, "CMOS active pixel image sensors for highly integrated imaging systems", *IEEE Journal of Solid-State Circuits*, vol. 32, no. 2, 1997, pp. 187-197.

- [14] S.G. Smith *et al.*, "A single-chip CMOS 306×244-pixel NTSC video camera and a descendant coprocessor device," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, December 1998, pp. 2104-2111.

- [15] M.J. Loinaz *et al.*, "A 200-mW, 3.3-V, CMOS color camera IC producing 352x288 24-b video at 30 Frames/s", *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, December 1998, pp. 2092-2103.

- [16] S. Agwani et al., "A 1/3-inch VGA CMOS imaging system on a chip", in Proc. 1999 IEEE Workshop on Charge Coupled Devices and Advanced Image Sensors, Nagano, Japan, pp. 21-24.

- [17] C. Cavadore, J. Solhusvik, P. Magnan, A. Gautrand, Y. Degerli, F. Lavernhe, J. Farré, O. Saint-Pé, R. Davancens, and M. Tulet, "Active pixel image sensors for space applications," *Proc. ESA 2nd Round Table on Micro/Nano-Technologies for Space*, WPP-132, Noordwijk, The Nederlands, October 1997, pp. 115-122.

- [18] C. Cavadore, J. Solhusvik, P. Magnan, A. Gautrand, Y. Degerli, F. Lavernhe, J. Farré, O. Saint-Pé, R. Davancens, and M. Tulet, "Design and characterization of CMOS APS imagers on two different technologies," *Proceedings of SPIE*, vol. 3301, January 1998 (San Jose, California), pp. 140-150.

- [19] P. Magnan, C. Cavadore, A. Gautrand, Y. Degerli, F. Lavernhe, J. Farré, O. Saint-Pé, R. Davancens, and M.Tulet, "Experimental characterization of CMOS APS imagers designed using two different technologies," *Proceedings of SPIE*, vol. 3410, May 1998 (Zurich, Switzerland), pp. 77-87.

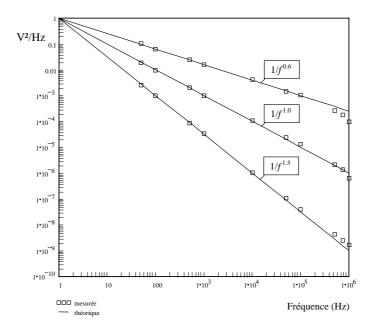

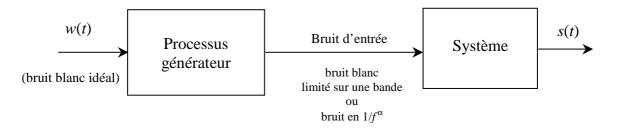

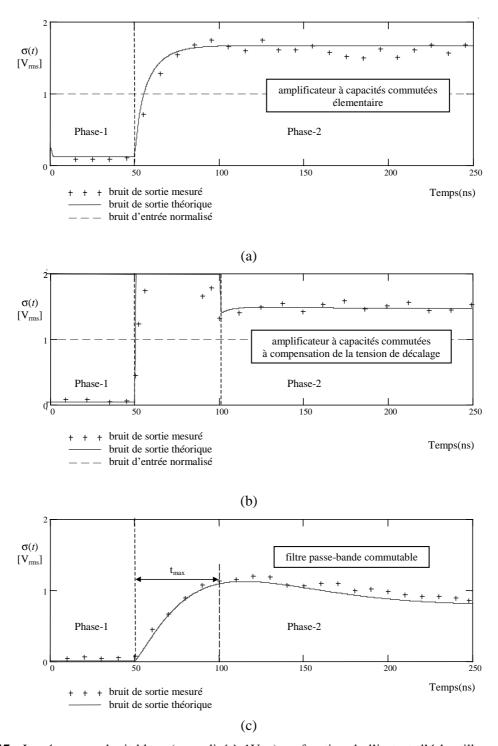

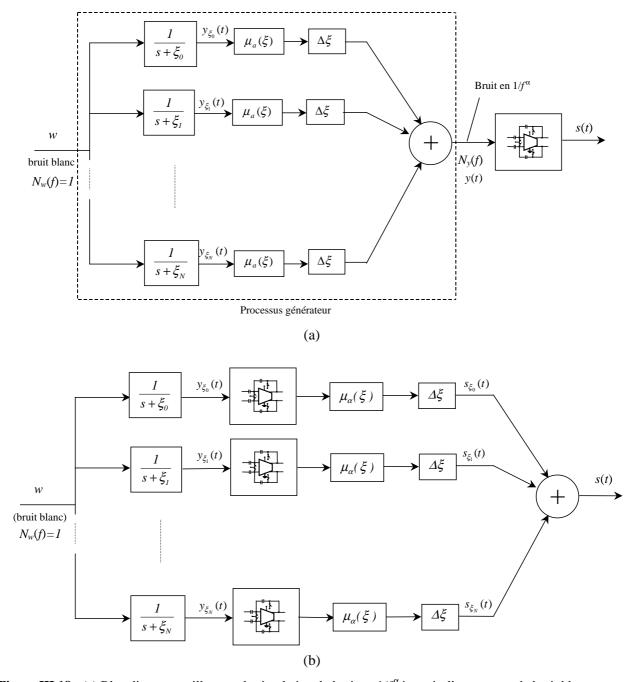

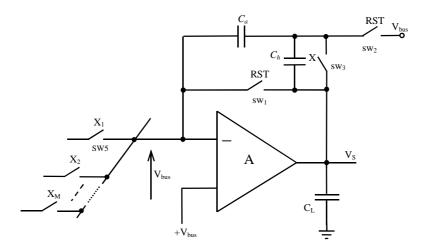

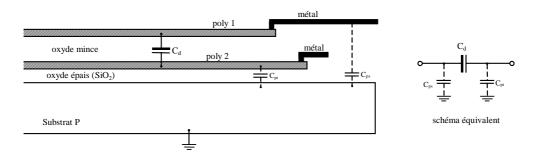

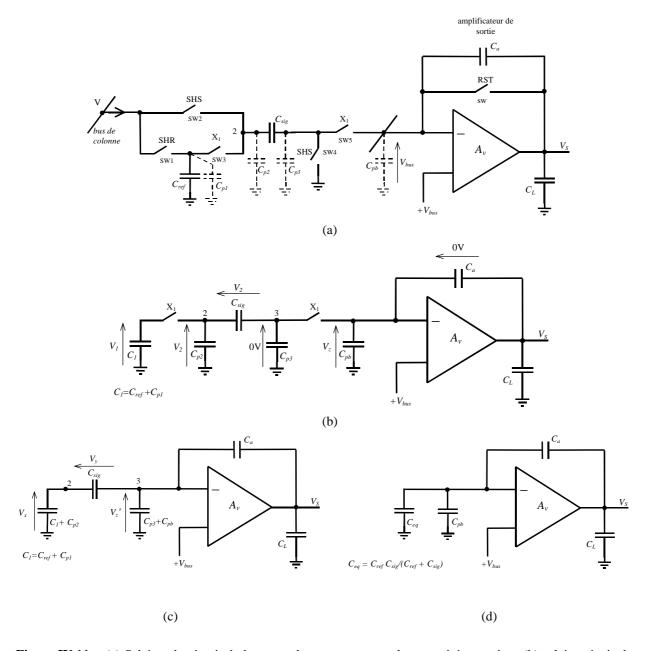

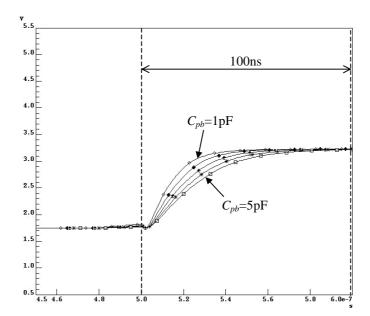

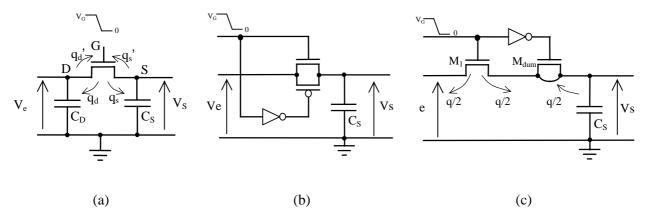

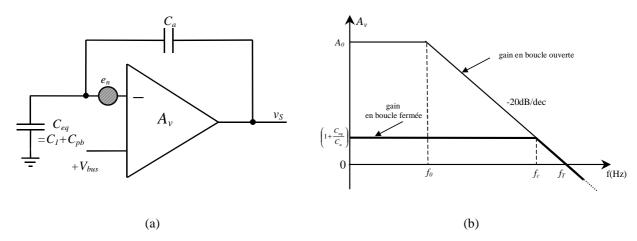

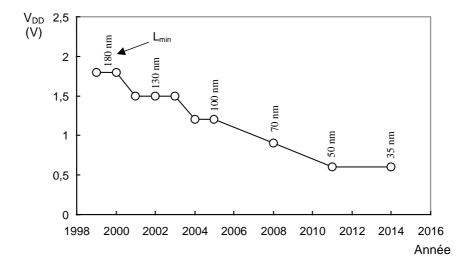

- [20] O. Saint-Pé, R. Davancens, M. Tulet, P. Magnan, C. Cavadore, A. Gautrand, Y. Degerli, F. Lavernhe, and J. Farré, "Development and characterization of active pixel sensors for space applications," *Proceedings of SPIE*, vol. 3440, July 1998 (San Diego, California), pp. 24-36.