## En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut Supérieur de l'Aéronautique et de l'Espace

## Présentée et soutenue par : Nathanaël SENSFELDER

le mercredi 31 mars 2021

## Titre :

Analyse et contrôle des interférences liées à la cohérence de cache dans les multi-coeurs COTS

**École doctorale et discipline ou spécialité :** ED MITT : Réseaux, télécom, système et architecture

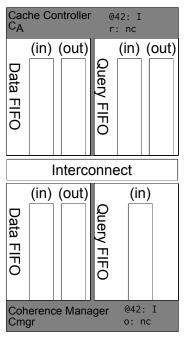

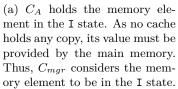

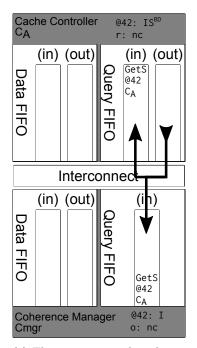

> **Unité de recherche :** Équipe d'accueil ISAE-ONERA MOIS

## Directeur(s) de Thèse :

Mme Claire PAGETTI (directrice de thèse) M. Julien BRUNEL (co-directeur de thèse)

### Jury :

Mme Christine ROCHANGE Professeure des Universités Université Toulouse III - Présidente

M. Björn BRANDENBURG Professeur des Universités Université de la Sarre - Examinateur

M. Julien BRUNEL Chargé de recherche ONERA - Co-directeur de thèse

Mme Janette CARDOSO Professeure ISAE-SUPAERO - Examinatrice

MI. Sylvain CONCHON Professeur des Universités Université Paris-Sud XI - Examinateuré

Mme Claire PAGETTI Maître de Recherche ONERA - Directrice de thèse

Mme Isabelle PUAUT Professeure des Universités Université de Rennes I - Rapporteure

M. Olivier H. ROUX Professeur des Universités École Centrale de Nantes - Rapporteur

## Abstract

This thesis proposes tools to help in the certification of multi-core processors for use in aeronautical systems. While the parallel nature of multi-core processors can greatly improve computation speeds, it also makes them difficult to predict, preventing their use in critical environments. Indeed, in such processors, the cores share access to nearly all resources and this causes conflicts, or interference, which lead to seemingly random variation in the execution time. Among the complex mechanisms prone to interference is cache coherence, which ensures that cores that use a same atomic memory block cannot blindly override the modifications made by another core and that all cores are made aware of all modifications. To achieve cache coherence, the processor automatically follows a predetermined protocol which defines messages to be generated according to the actions of a core, as well as the actions to be performed when another core's message is received.

The focus of this thesis is to identify the interference generated by the cache coherence mechanisms and provide a way to predict their effects on the applications, as a first step toward their mitigation. The first contribution made is to address the ambiguities in the understanding applicants have of the coherence protocol implemented on their chosen architecture. Indeed, architecture documentation does not generally offer sufficient details on their cache coherence protocol. This thesis proposes a formalization of some standard cache protocols and a strategy relying on micro-benchmarks in order to clarify the implementation details of the architecture's protocol. This approach is applied to the NXP QorIQ T4240 architecture. Once the protocol has been correctly identified, the second contribution consists in the making of a low-level description of the architecture using timed automata in order to adequately represent the micro-behaviors and understand clearly how the cache coherence protocol acts. In effect, a generic model generation framework has been developed, capable of handling cache coherence protocols as described by the applicant, and to support architectures with different configurations in order to better fit the applicant's chosen architecture. The third contribution explains how to make use of the timed automata low-level representation of the architecture to expose interference. It proposes a strategy to detail the causes and effects of cache coherence interference on the given programs. Starting from a simple analysis of execution time, the results go down to instruction level, indicating how each instruction generates and suffers from interference. This is intended to provide sufficient information on cache coherence interference to the applicant, both for the purposes of certification and to form the base upon which a mitigation strategy can be started.

In effect, this thesis provides the applicant with the means to understand the cache coherence mechanisms used by their chosen architecture and to expose the interference they generate.

## Résumé Français

L'objectif de cette thèse est d'offrir des outils d'aide à la certification aéronautique de processeurs COTS multi-cœurs. Ces architectures sont par nature parallèles et peuvent de ce fait largement améliorer les performances de calcul. Cependant elles souffrent d'un grand manque de prédictibilité, au sens où calculer les pires d'exécution même pour des programmes simples est un problème complexe, voire impossible dans le cas général. En effet, les cœurs partagent l'accès à presque toutes les ressources ce qui provoque des conflits (qualifiés d'interférences) entrainant des variations non maîtrisées des temps d'exécutions. Parmi les mécanismes complexes d'un processeur multi-coeur se trouve la cohérence de caches. Celle-ci assure que tous les cœurs lisant ou écrivant dans un même bloc mémoire ne peuvent pas aveuglement ignorer les modifications appliquées par les autres. Afin de maintenir la cohérence de caches, le processeur suit un protocole pré-déterminé qui définit les messages à envoyer en fonction des actions d'un cœur ainsi que les actions à effectuer lors de la réception du message d'un autre cœur.

Cette thèse porte sur l'identification des interférences générées par les mécanismes de cohérence de caches ainsi que sur les moyens de prédiction de leurs effets sur les applications en vue de réduire les effets négatifs temporels. La première contribution adresse les ambiguïtés dans la compréhension que les applicants ont de la cohérence de cache réellement présente dans l'architecture. En effet, la documentation des architectures ne fournit généralement pas suffisamment de détails sur les protocoles. Cette thèse propose une formalisation des protocoles standards, ainsi qu'une stratégie, reposant sur les micro-benchmarks, pour clarifier les choix d'implémentation du protocole de cohérence présent sur l'architecture. Cette stratégie a notamment été appliquée sur le NXP QorIQ T4240. Une fois le protocole correctement identifié, la seconde contribution consiste à réaliser une description basniveau de l'architecture en utilisant des automates temporisés afin de représenter convenablement les micro-comportements et comprendre clairement comment le protocole de cohérence de cache agit. Ainsi, un framework de génération de modèles génériques a été développé, capable de supporter plusieurs protocoles de cohérence de cache et de représenter différents agencements d'architectures afin de mieux correspondre à l'architecture choisie par le postulant. La troisième contribution explique comment utiliser cette représentation de l'architecture pour exhiber les interférences. Elle propose une stratégie pour détailler les causes et effets de chaque interférence liée à la cohérence de caches sur les programmes. Commençant par une simple analyse de temps d'exécution, les résultats descendent jusqu'au niveau des instructions pour indiquer comment chaque instruction génère et souffre des interférences. L'objectif étant alors de fournir suffisamment d'information à l'appliquant à la fois pour la certification, mais aussi pour définir une stratégie d'atténuation et de maîtrise des effets temporels.

Ainsi, cette thèse fournit l'appliquant des outils pour comprendre les mécanismes de cohérence de cache présent sur une architecture donnée et pour exhiber les interférences associées.

# Contents

| Ι        | Co                               | ontext                                                                                              | 13                                |

|----------|----------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------|

| 1        | <b>Intr</b><br>1.1<br>1.2<br>1.3 | coduction         Context                                                                           | <b>15</b><br>15<br>15<br>17<br>17 |

| <b>2</b> | (Tir                             | med) Automata                                                                                       | 19                                |

|          | 2.1                              | Classical Automata                                                                                  | 19<br>19<br>22                    |

|          | 2.2                              | UPPAAL and Networks of Timed Automata2.2.1System Definition2.2.2Query Logic Operators and Semantics | 23<br>23<br>27                    |

|          | 2.3                              | Conclusion                                                                                          | 27                                |

| 3        | Fun                              | damentals of Cache Coherence                                                                        | 29                                |

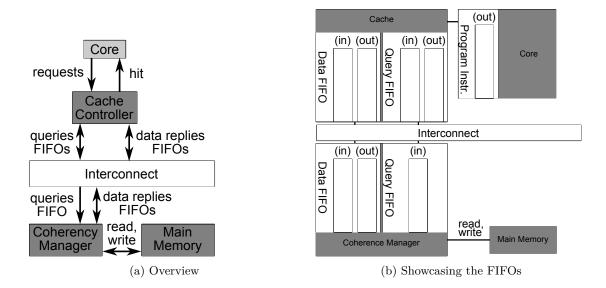

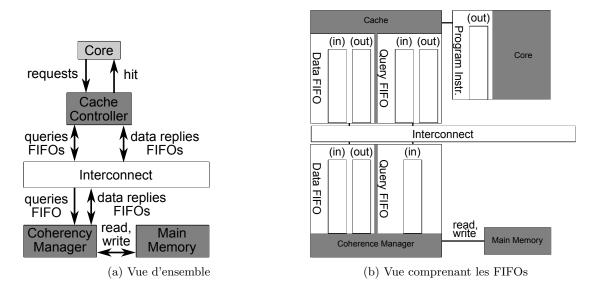

| 0        | 3.1                              | Components                                                                                          | <b>29</b>                         |

|          | 0.1                              | 3.1.1 Memory Elements                                                                               | $\frac{29}{29}$                   |

|          |                                  | 3.1.2 Core: Programs & Instructions                                                                 | $\frac{29}{30}$                   |

|          |                                  | 3.1.3 Caches                                                                                        | 31                                |

|          |                                  | 3.1.4 Coherence Manager                                                                             | 32                                |

|          |                                  | 3.1.5 Interconnect                                                                                  | 33                                |

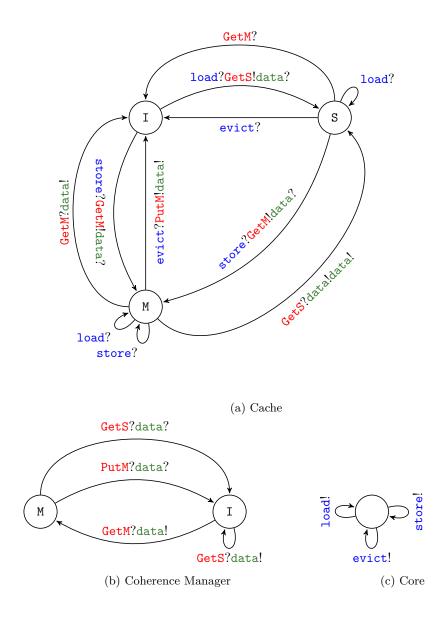

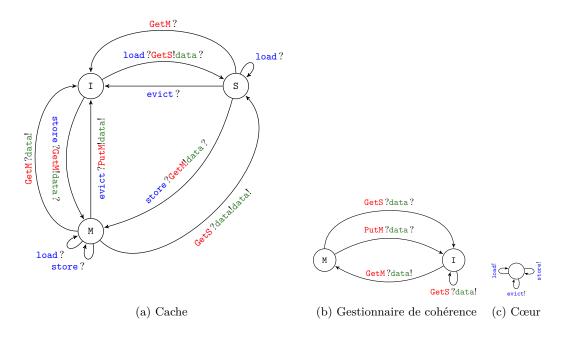

|          | 3.2                              | Coherence Protocols                                                                                 | 34                                |

|          |                                  | 3.2.1 Introduction to the MSI Protocol                                                              | 34                                |

|          |                                  | 3.2.2 Properties to be Verified                                                                     | 36                                |

|          |                                  | 3.2.3 Protocol Definition                                                                           | 37                                |

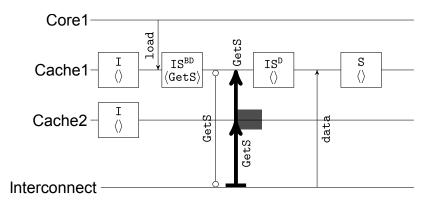

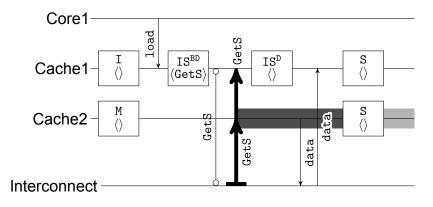

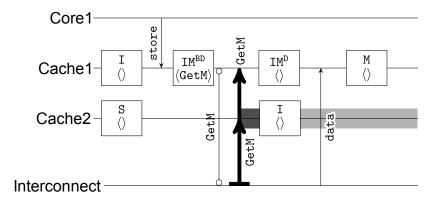

|          | 3.3                              | Split-Transaction Bus, case of the MSI Protocol                                                     | 37                                |

|          |                                  | 3.3.1 State Naming                                                                                  | 37                                |

|          |                                  | 3.3.2 Examples                                                                                      | 40                                |

|          | 3.4                              | Variants                                                                                            | 49                                |

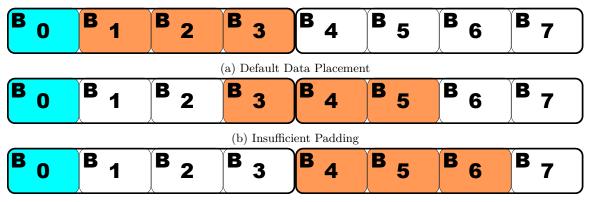

|          | 3.5                              | Cache Line Organization                                                                             | 49                                |

|          |                                  | 3.5.1 Replacement Policies                                                                          | 49                                |

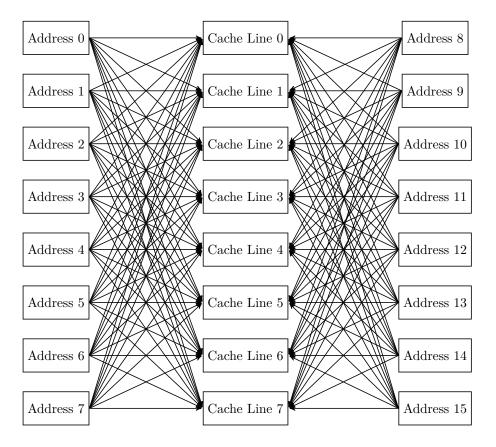

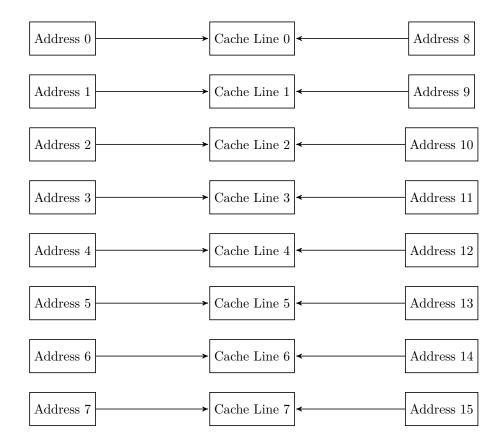

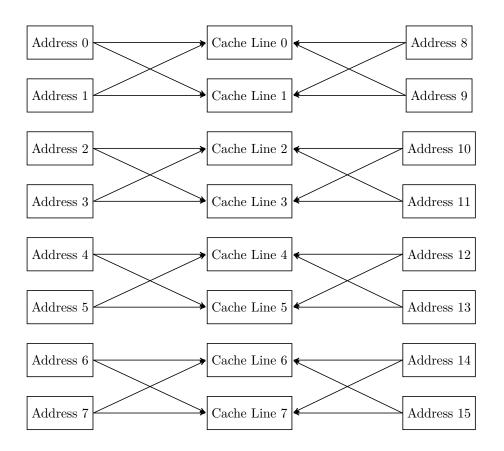

|          |                                  | 3.5.2 Placement Policies                                                                            | 50                                |

|          | 3.6                              | Conclusion                                                                                          | 54                                |

### CONTENTS

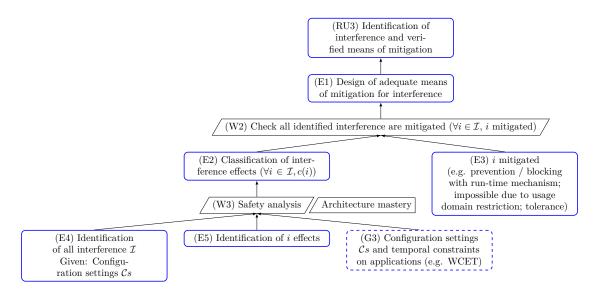

| <b>4</b> | Obj | ective                                                                                          | 55       |

|----------|-----|-------------------------------------------------------------------------------------------------|----------|

|          | 4.1 | Tasks Required of the Applicant                                                                 | 55       |

|          |     | 4.1.1 Coherence Protocol Identification                                                         | 55       |

|          |     | 4.1.2 Measuring the Impact of Interference of the Software                                      | 56       |

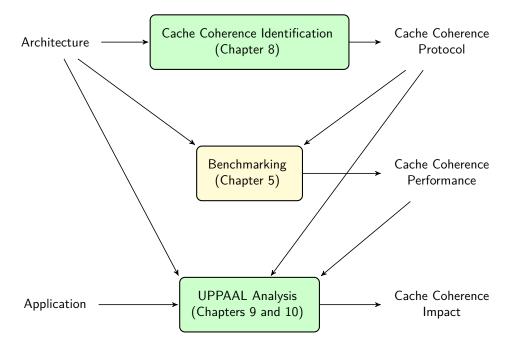

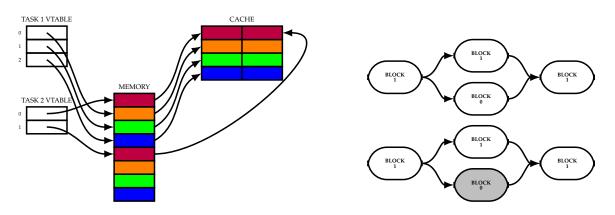

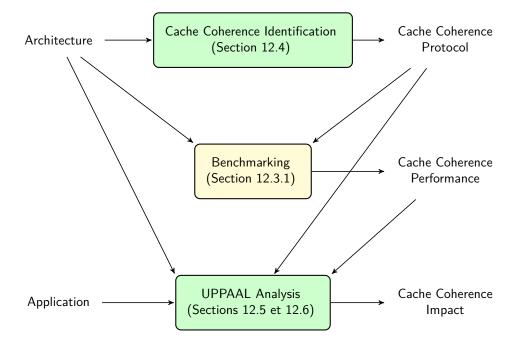

|          | 4.2 | Proposed Solution                                                                               | 57       |

|          |     | 4.2.1 Hypotheses and Limitations                                                                | 57       |

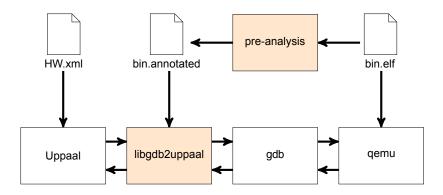

|          |     | 4.2.2 Framework Overview                                                                        | 59       |

|          | 4.3 | Conclusion                                                                                      | 60       |

|          | 1.0 |                                                                                                 | 00       |

| II       | R   | elated Works                                                                                    | 61       |

| 5        | Mic | cro-Stressing Benchmarks                                                                        | 63       |

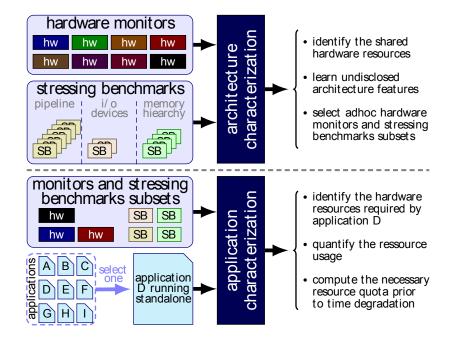

|          | 5.1 | Detecting Component Correlation                                                                 | 64       |

|          |     | 5.1.1 Evaluating Interference Through Resource-Stressing                                        | 64       |

|          |     | 5.1.2 Architecture and Application Characterization                                             | 67       |

|          | 5.2 | Analyzing Cache Performance                                                                     | 69       |

|          |     | 5.2.1 Cost of Cache Coherence                                                                   | 69       |

|          |     | 5.2.2 Cache Performance Analysis                                                                | 71       |

|          | 5.3 | Finding Elusive Hardware Monitors                                                               | 74       |

|          | 5.4 | Conclusion                                                                                      | 75       |

| 6        | Цат | ndling Cache Interference in Safety-Critical Systems                                            | 77       |

| U        | 6.1 | Through Restrictions                                                                            | 77       |

|          | 0.1 | 6.1.1 Shared Cache Partitioning                                                                 | 77       |

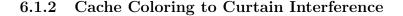

|          |     | 6.1.2       Cache Coloring to Curtain Interference                                              | 78       |

|          |     | 6.1.2       Cache Coloring to Curtain Interference         6.1.3       Limited Shared Resources | 78<br>78 |

|          |     |                                                                                                 | 78<br>79 |

|          | 6.9 |                                                                                                 |          |

|          | 6.2 | Through Hardware Modifications                                                                  | 80       |

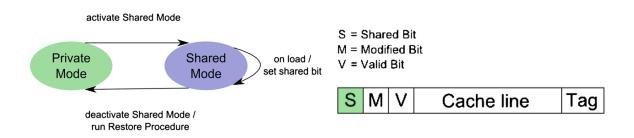

|          |     | 6.2.1 Predictable MSI                                                                           | 80       |

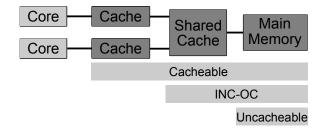

|          |     | 6.2.2 Limited Cacheability                                                                      | 82       |

|          |     | 6.2.3 On-Demand Cache Coherence                                                                 | 83       |

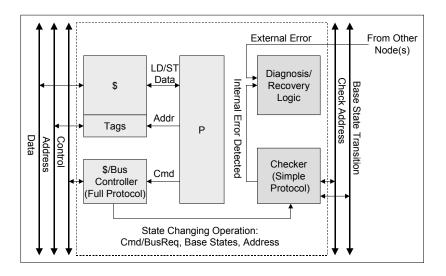

|          |     | 6.2.4 Dynamic Verification of Cache Coherence                                                   | 84       |

|          | 6.3 | By Accepting It                                                                                 | 85       |

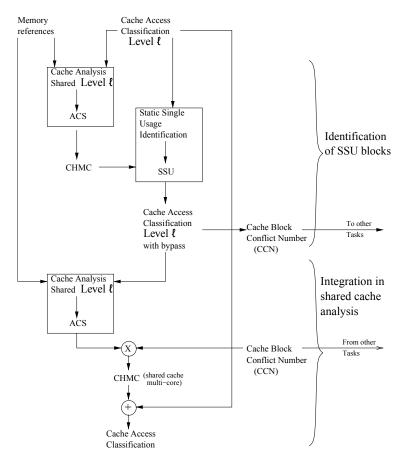

|          |     | 6.3.1 Instruction Cache Analysis                                                                | 85       |

|          |     | 6.3.2 Data Cache Analysis                                                                       | 88       |

|          | 6.4 | Conclusion                                                                                      | 89       |

| 7        | Ana | alyzing Performance Through Formal Methods                                                      | 91       |

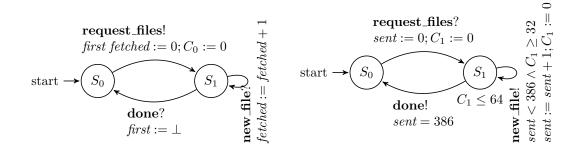

|          | 7.1 | Single-Core Processors                                                                          | 91       |

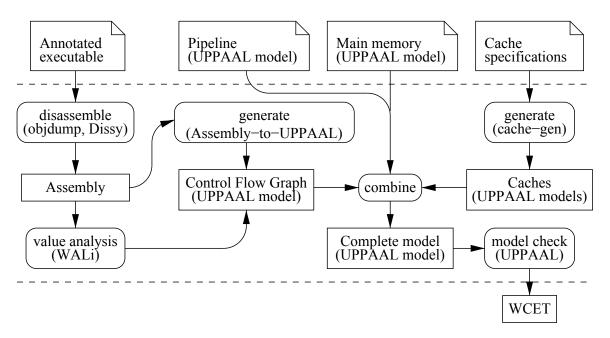

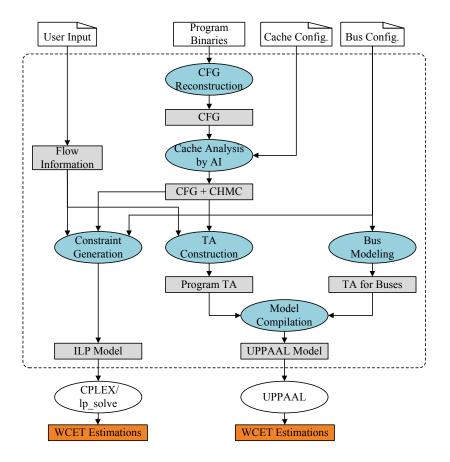

|          |     | 7.1.1 METAMOC                                                                                   | 91       |

|          |     | 7.1.2 WUPPAAL                                                                                   | 94       |

|          | 7.2 | Multi-Core Processors                                                                           | 96       |

|          |     | 7.2.1 Modeling Shared Buses                                                                     | 96       |

|          |     | 7.2.2 Multi-Core Analysis using only UPPAAL                                                     | 98       |

|          | 7.3 | Conclusion                                                                                      | 100      |

|          | -   |                                                                                                 |          |

| II | [ ( | Contri   | ibutions                                                 | 103 |

|----|-----|----------|----------------------------------------------------------|-----|

| 8  | Ide | ntifying | g Cache Coherence                                        | 105 |

|    | 8.1 | Identif  | fication Strategy                                        | 106 |

|    |     | 8.1.1    | Defining the Hypothetical Cache Coherence Protocol       | 106 |

|    |     | 8.1.2    | Defining the Observable Cache Coherence Protocol         | 106 |

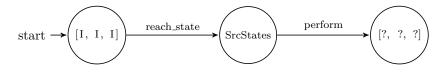

|    |     | 8.1.3    | Naive Exploration of the Observable Protocol             | 108 |

|    |     | 8.1.4    | State Exploration & Reachability                         | 109 |

|    |     | 8.1.5    | Matching Observed States with Hypothetical States        | 109 |

|    |     | 8.1.6    | Activity Comparison                                      | 111 |

|    |     | 8.1.7    | Exploration Guided by Hypothetical Protocol              | 112 |

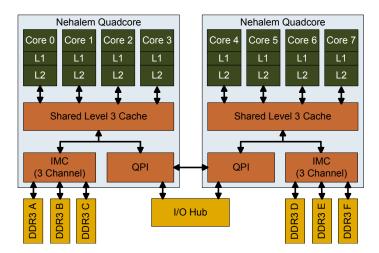

|    | 8.2 | Bench    | mark Implementation                                      | 113 |

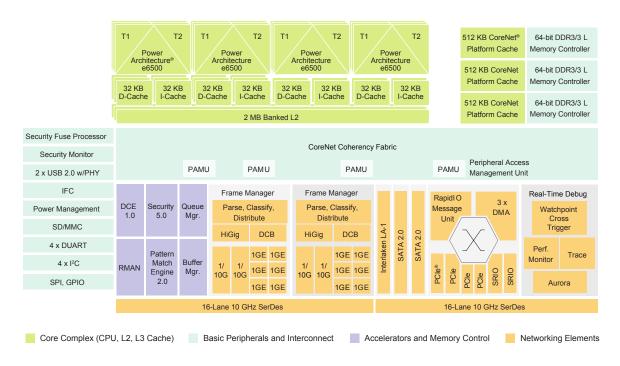

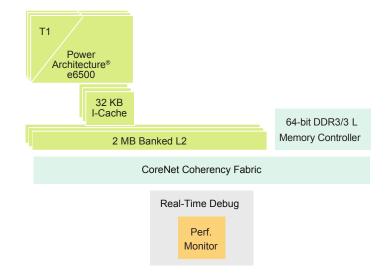

|    |     | 8.2.1    | The NXP QorIQ T4240                                      | 113 |

|    |     | 8.2.2    | Naught                                                   | 114 |

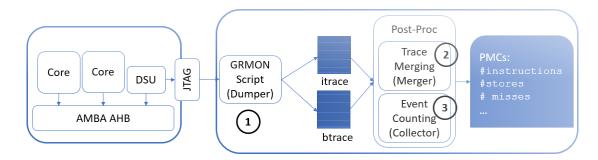

|    |     | 8.2.3    | Initializing the Caches (Lines 1 & 2 of Figure 8.4)      | 115 |

|    |     | 8.2.4    | Enabling the Performance Monitors (Line 3 of Figure 8.4) | 116 |

|    |     | 8.2.5    | Performing Instructions (Lines 4 & 5 of Figure 8.4)      |     |

|    |     | 8.2.6    | Data Recording (Lines 6 & 7 of Figure 8.4)               | 117 |

|    | 8.3 | Hypot    | hetical Split-Transaction MESI Protocol                  | 118 |

|    |     | 8.3.1    | Strategy Application for a MESI Protocol                 | 120 |

|    |     | 8.3.2    | Coherence State Matching                                 |     |

|    |     | 8.3.3    | Coherence Activity Matching                              |     |

|    | 8.4 | Hypot    | hetical Split-Transaction MESIF Protocol                 | 122 |

|    |     | 8.4.1    | Strategy Application for a MESIF Protocol                | 124 |

|    |     | 8.4.2    | No store Optimization on F                               | 124 |

|    |     | 8.4.3    | Odd Results with evict on M                              |     |

|    |     | 8.4.4    | Better Coherence Manager                                 | 125 |

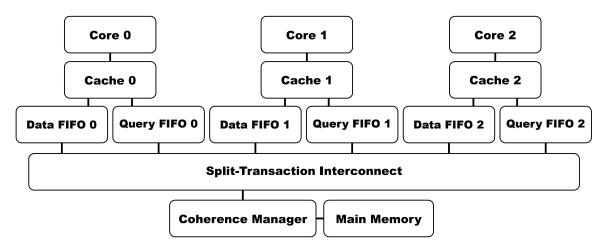

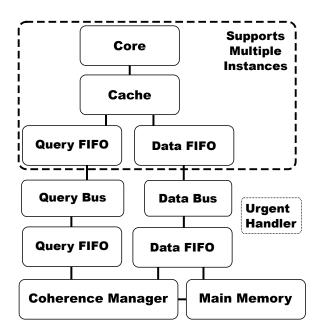

#### Cache Col Modeling

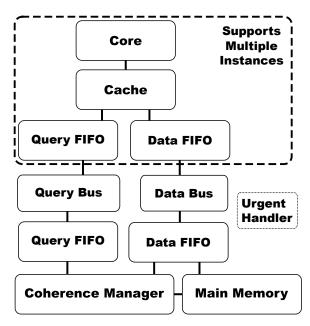

| Mo  | deling | Cache Coherence            | 127 |

|-----|--------|----------------------------|-----|

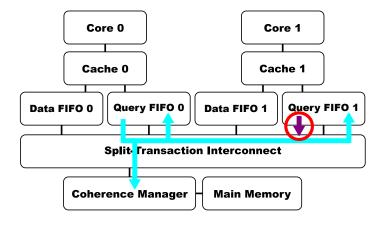

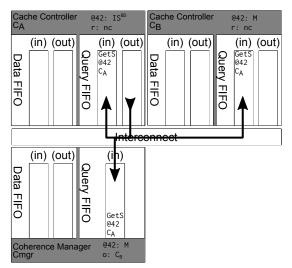

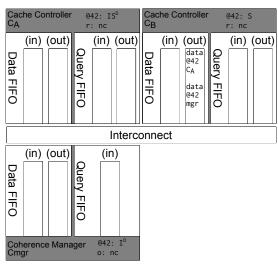

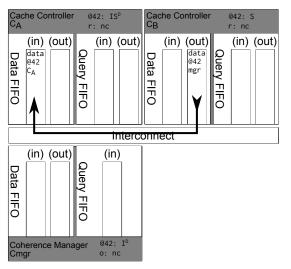

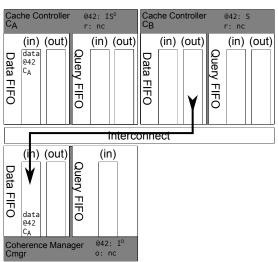

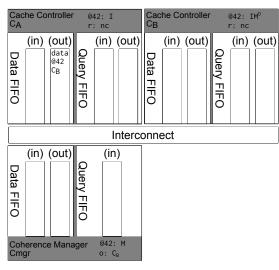

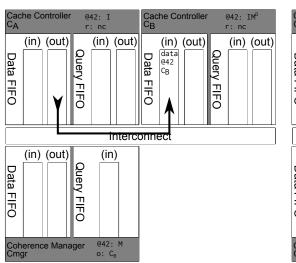

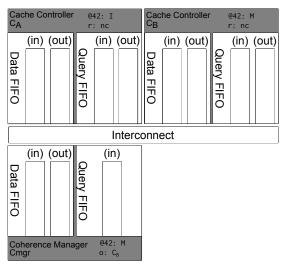

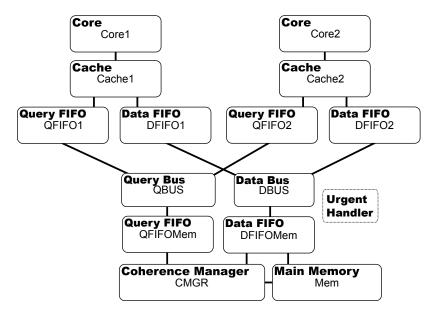

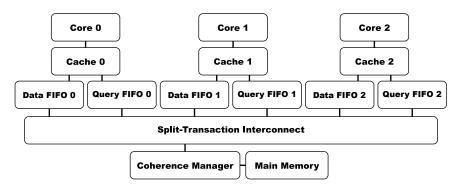

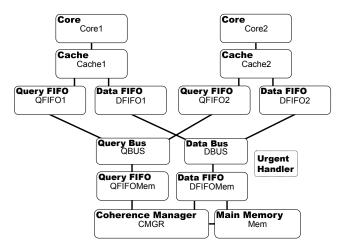

| 9.1 | Model  | ling Strategy              | 127 |

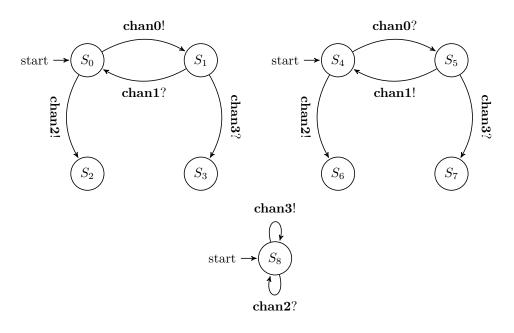

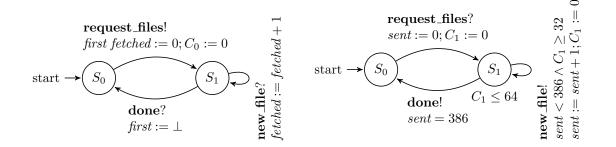

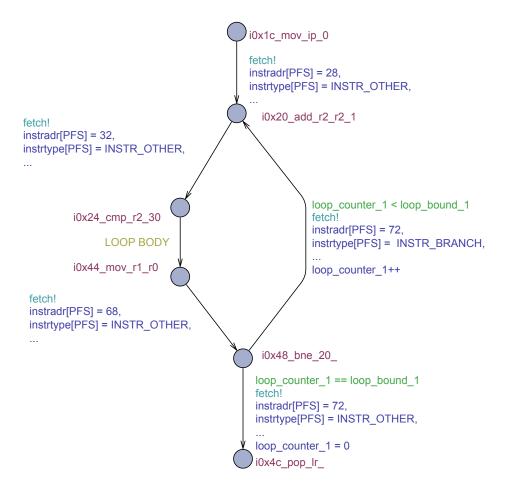

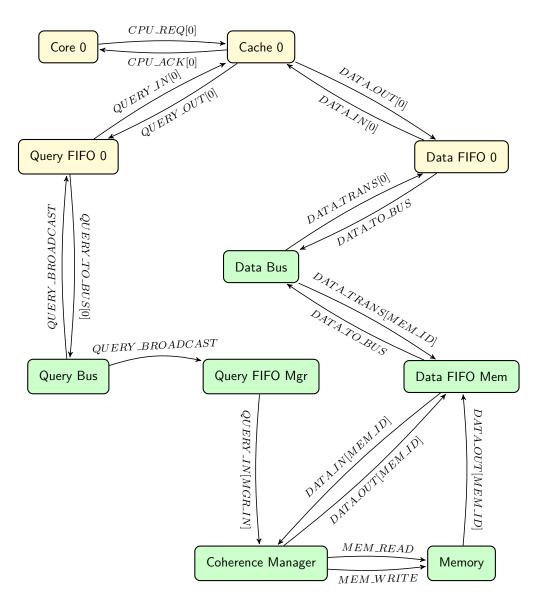

| 9.2 | Synch  | ronization Channels        | 129 |

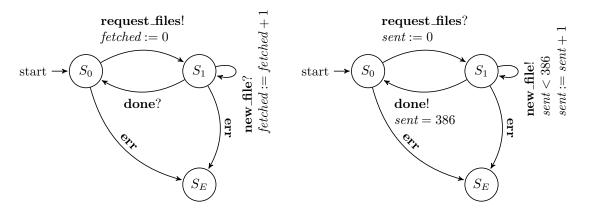

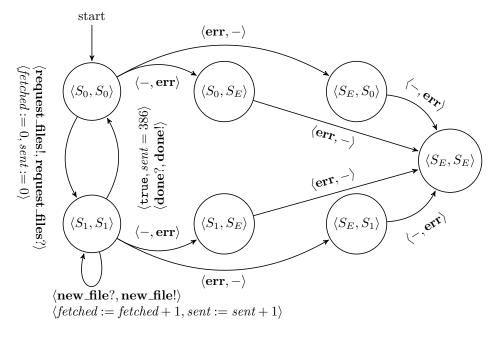

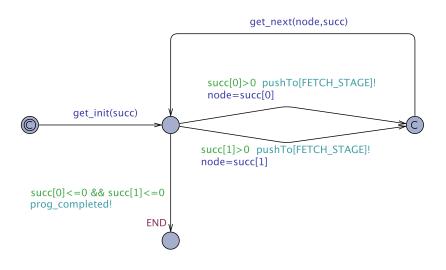

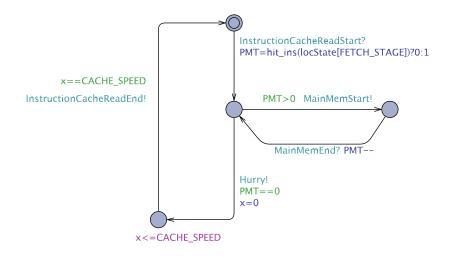

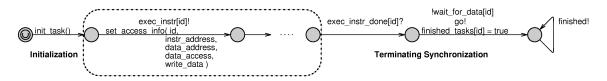

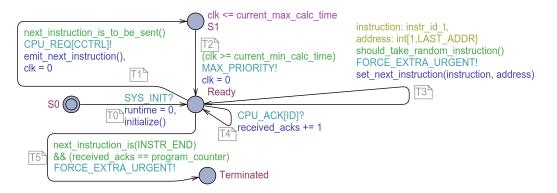

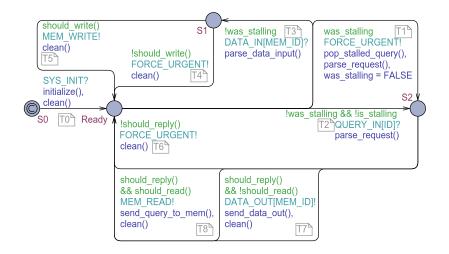

| 9.3 | Model  | ls of Core and Programs    | 132 |

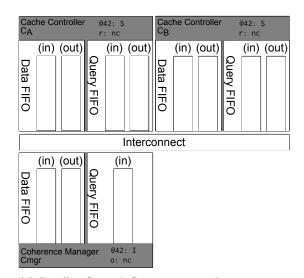

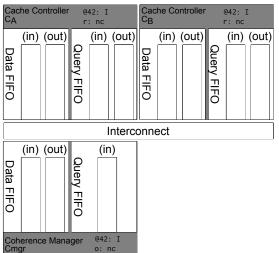

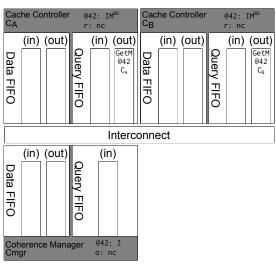

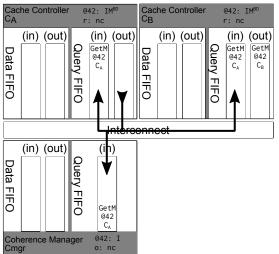

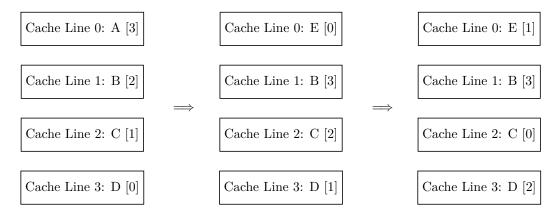

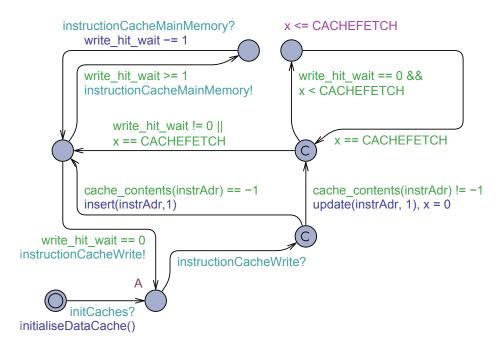

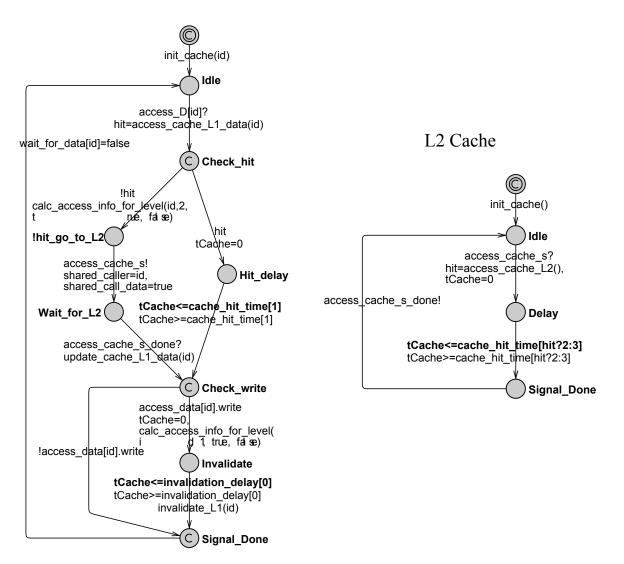

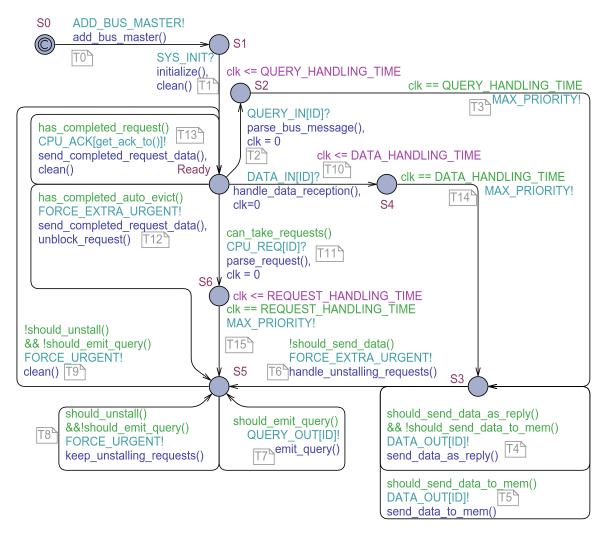

| 9.4 | Model  | l of the Caches            | 134 |

|     | 9.4.1  | Initialization             | 135 |

|     | 9.4.2  | Cache Lines                | 136 |

|     | 9.4.3  | Modeling the LRU policy    | 137 |

|     | 9.4.4  | Handling Requests          | 137 |

|     | 9.4.5  | Handling Messages          | 139 |

|     | 9.4.6  | Modeling Actions           | 140 |

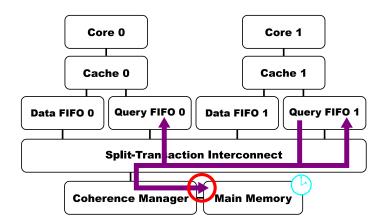

| 9.5 | Model  | ls of FIFOs                | 141 |

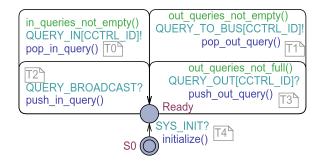

|     | 9.5.1  | Query FIFO                 | 141 |

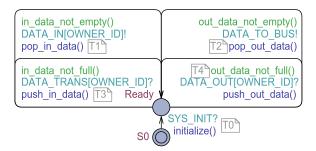

|     | 9.5.2  | Data FIFO                  | 142 |

| 9.6 | Model  | l of the Interconnect      | 143 |

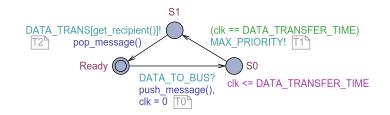

|     | 9.6.1  | Data Bus                   | 144 |

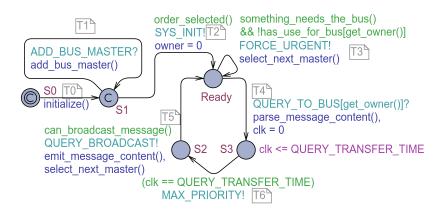

|     | 9.6.2  | Query Bus                  | 144 |

| 9.7 | Model  | l of the Coherence Manager | 146 |

|     | 9.7.1  | Modeling Actions           | 149 |

### CONTENTS

177

|    | 9.8  | Model of the Memory 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9 |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

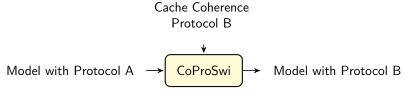

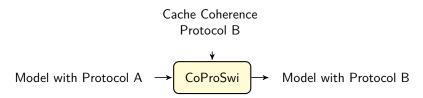

|    | 9.9  | Switching Coherence Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

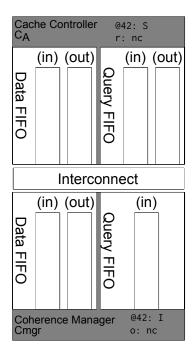

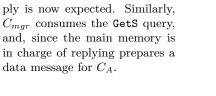

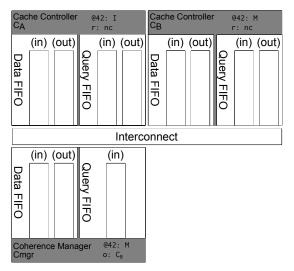

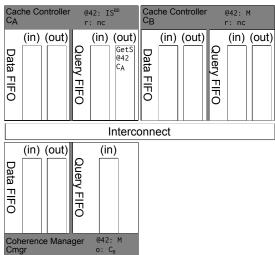

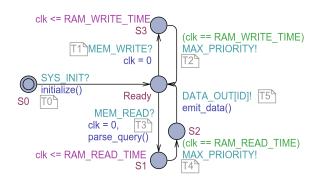

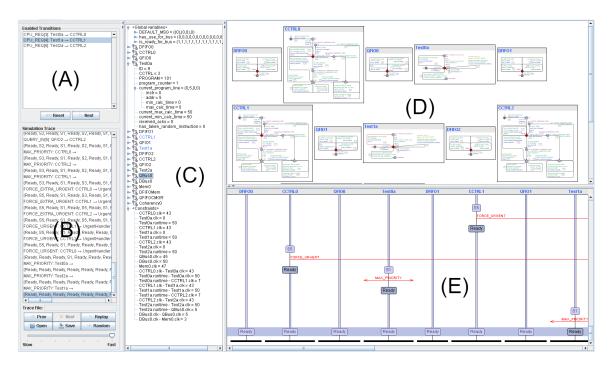

|    | 9.10 | Step-by-Step Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 |

|    | 9.11 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 |

| 10 | Exp  | osing Interference 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 |

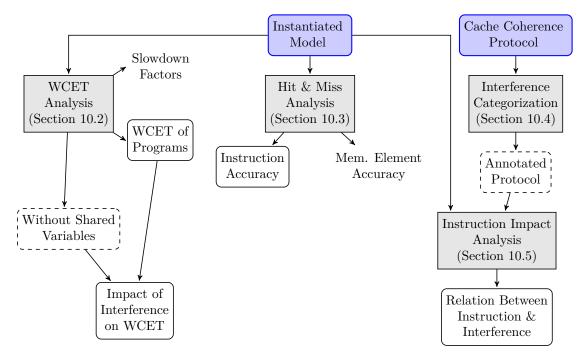

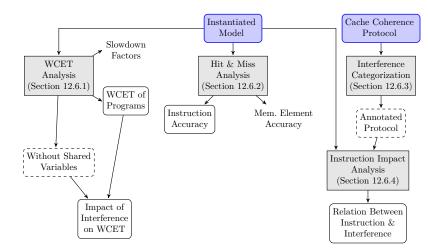

|    | 10.1 | Overview of the Analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5 |

|    | 10.2 | Analyzing Impact on Program Execution Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 |

|    | 10.3 | Analyzing Impact on Hit & Miss 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9 |

|    |      | 10.3.1 Hit and Miss in the Model $\ldots$ 160 $\ldots$ | 0 |

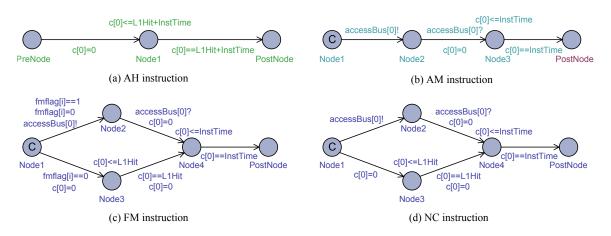

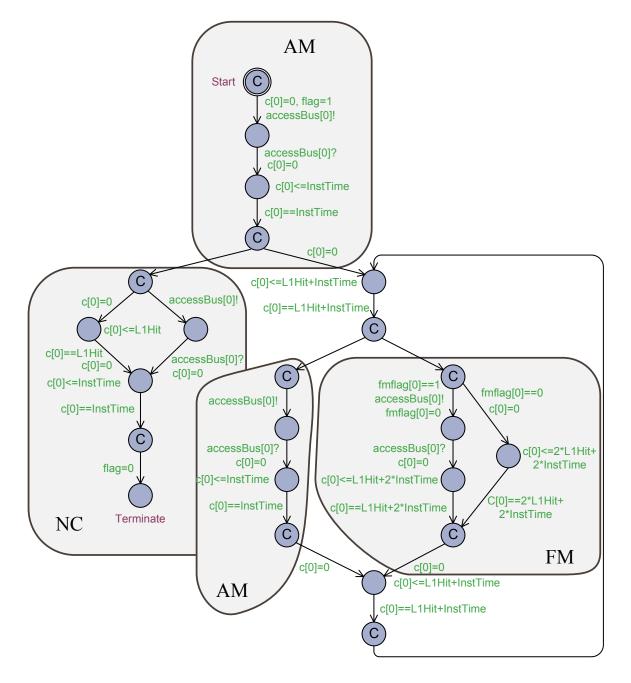

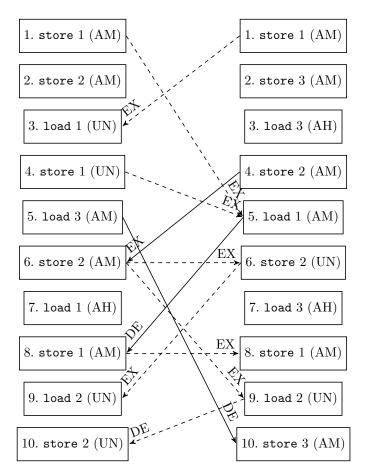

|    |      | 10.3.2 Instruction Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 |

|    |      | 10.3.3 Memory Element Accuracy Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 |

|    | 10.4 | Defining Impact of External Queries 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 |

|    |      | 10.4.1 Minor Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |

|    |      | 10.4.2 Demoting Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 |

|    |      | 10.4.3 Expelling Interference 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6 |

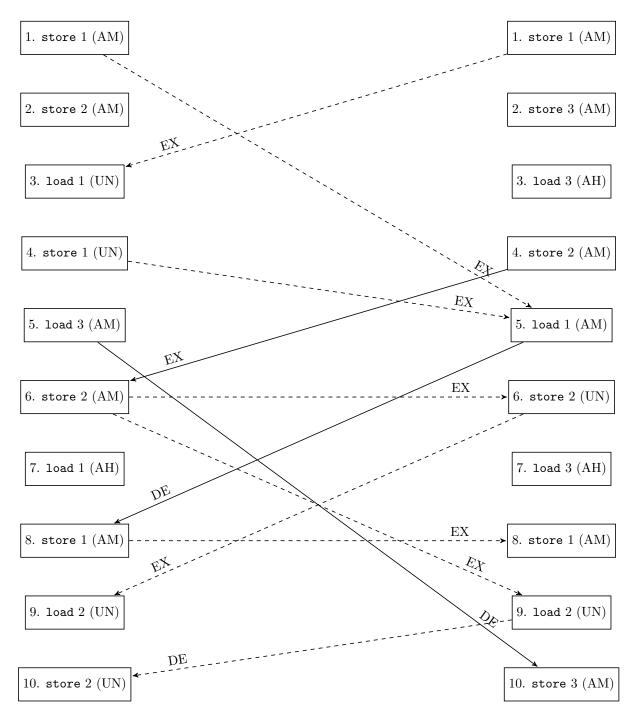

|    |      | 10.4.4 Protocol Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 |

|    | 10.5 | Analyzing Impact of Intructions on Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 |